Specific Process Knowledge/Lithography/UVLithography: Difference between revisions

| Line 46: | Line 46: | ||

[[Specific_Process_Knowledge/Lithography/Coaters#Spin_coater:_Manual_Labspin|Spin coater: Manual Labspin]] | [[Specific_Process_Knowledge/Lithography/Coaters#Spin_coater:_Manual_Labspin|Spin coater: Manual Labspin]] | ||

| | |[[Specific_Process_Knowledge/Lithography/UVExposure#KS_Aligner|KS Aligner]], | ||

[[Specific_Process_Knowledge/Lithography/UVExposure#Aligner:_MA6_-_2|Aligner: MA6 - 2]] or | |||

[[Specific_Process_Knowledge/Lithography/UVExposure#Aligner-6inch|Aligner-6inch]] | |||

|[[Specific_Process_Knowledge/Lithography/Development#Developer-6inch|AZ 351B developer]] | |[[Specific_Process_Knowledge/Lithography/Development#Developer-6inch|AZ 351B developer]] | ||

Revision as of 12:52, 11 November 2014

Feedback to this page: click here

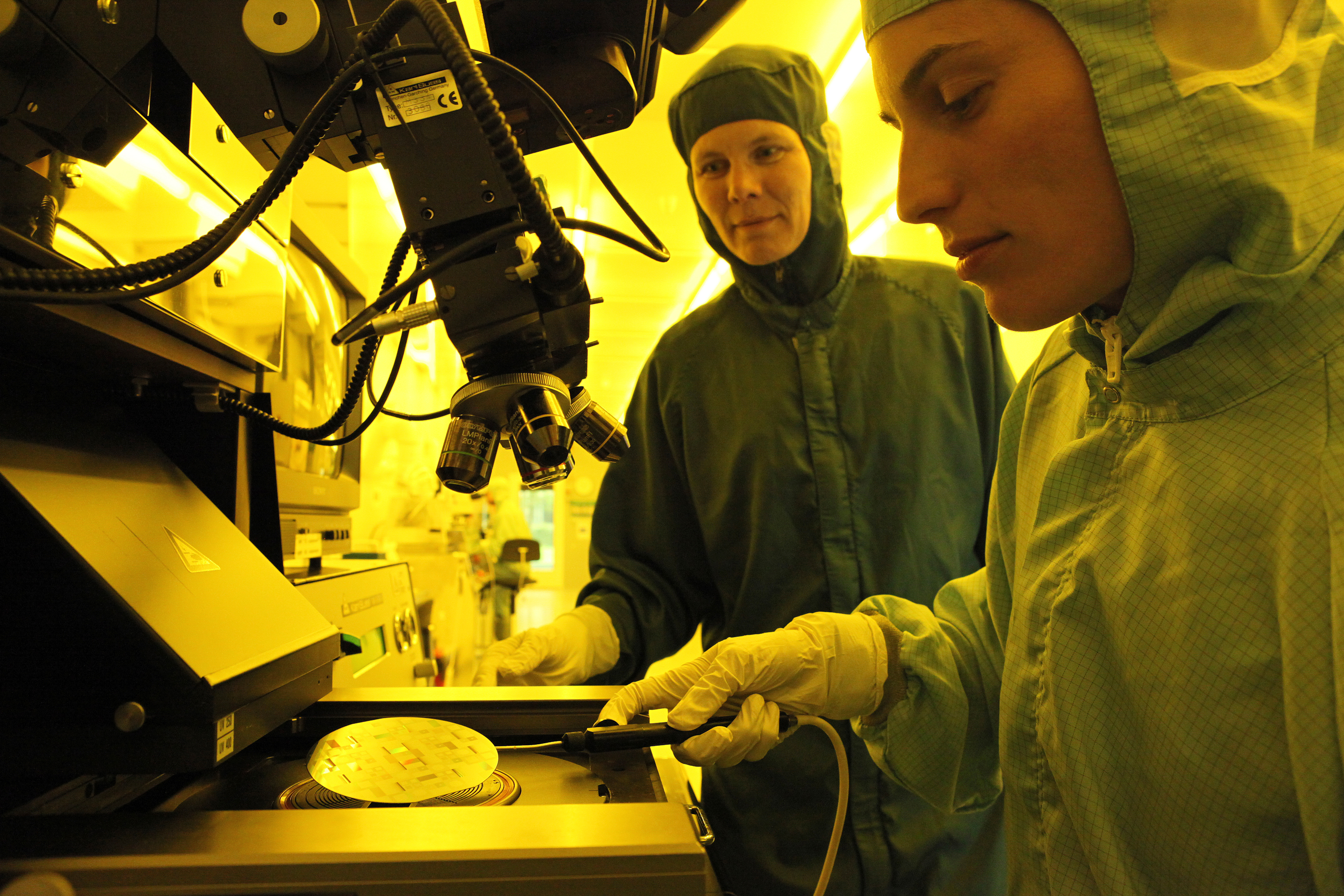

UV Lithography uses ultraviolet light to transfer a pattern from a mask to a wafer coated with photoresist. The photoresist film is spin coated on the wafers and the pattern is transferred to the wafer by using a mask aligner. DTU Danchip houses a number of automatic or semi-automatic coaters and mask aligners.

Mask Design

In order to realize your device you will need a way to draw the patterns that define the structures in the different layers on the wafer. This is done in a drawing tool for mask layout. The output is a file you send to a mask house, which in return supplies you with a number of photolithographic masks. Each mask is a glass plate with a chromium pattern that mimics a layer in your layout.

Please read more details here: Mask Design

Resist Overview

| Resist | Polarity | Manufacturer | Comments | Technical reports | Spin Coating | Exposure | Developer | Rinse | Remover | Process flows (in docx-format) |

| AZ 5214E | Positive but the image can be reversed | AZ Electronic Materials | Can be used for both positive and reverse processes with resist thickness between 1 and 4 µm. | AZ5214E.pdf | SSE,

KS Spinner or |

KS Aligner, | AZ 351B developer

or |

DI water | Acetone | |

| AZ 4562 | Positive | AZ Electronic Materials | For process with resist thickness between 6 and 25 µm. | AZ4500.pdf | SSE or | 28 mJ/cm2 per µm resist for i-line, probably increasing with increasing thickness.

Multiple exposure recommended. ½ dose for broadband exposure. |

AZ 351B developer

or |

DI water | Acetone | Process_Flow_thick_AZ4562.docx |

| AZ MiR 701 | Positive | AZ Electronic Materials | High selectivity for dry etch. | AZ_MiR_701.pdf | Spin Track 1 + 2 | Preliminary results:

105 mJ/cm2 per µm resist for i-line. 1/5 dose for broadband exposure. |

AZ 726 MIF developer | DI water | Remover 1165 | Process_Flow_AZ_MiR701.docx |

| AZ nLOF 2020 | Negative | AZ Electronic Materials | Negative sidewalls for lift-off. | AZ_nLOF_2020.pdf | Spin Track 1 + 2 | <30 mJ/cm2 per µm resist for i-line, decreasing with increasing thickness.

Same dose for broadband exposure. |

AZ 726 MIF developer | DI water | Remover 1165 | Process_Flow_AZ_nLOF_2020.docx |

| SU-8 | Negative | Microchem | SU-8_DataSheet_2005.pdf, SU-8_DataSheet_2075.pdf | KS Spinner | Thickness and process dependent.

Refer to process datasheet and literature. |

mr-Dev 600 developer (PGMEA) | IPA | Plasma ashing can remove crosslinked SU8. | Process_Flow_SU8_70um.docx |