Specific Process Knowledge/Lithography/nLOF: Difference between revisions

| Line 29: | Line 29: | ||

==PEB baking time investigation== | ===PEB baking time investigation=== | ||

While 60 s @ 110°C is adequate for Si substrates, less thermally conductive substrates (glass, III-V materials, chips bonded to carrier), have shown problems using the standard PEB recipe.<br> | While 60 s @ 110°C is adequate for Si substrates, less thermally conductive substrates (glass, III-V materials, chips bonded to carrier), have shown problems using the standard PEB recipe.<br> | ||

These problems were largely solved by increasing the PEB time to 120 s. Tests (on Aligner: Maskless 02) have shown that the lithographic performance of nLOF on Si is improved when using 120 s @ 110°C PEB (less stitching, less bias, more negative profile). | These problems were largely solved by increasing the PEB time to 120 s. Tests (on Aligner: Maskless 02) have shown that the lithographic performance of nLOF on Si is improved when using 120 s @ 110°C PEB (less stitching, less bias, more negative profile). | ||

Revision as of 09:10, 9 April 2025

Specific Process Knowledge/Lithography/authors generic

Feedback to this page: click here

Resist description

AZ nLOF 2020 is a negative UV photoresist, suitable for lift-off processes.

Spin coating

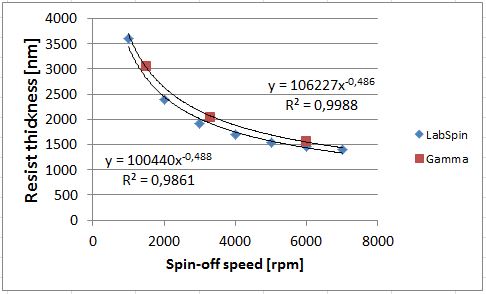

Typical spin parameters:

- Spin off: 30-60 s

- Soft bake: 60 s @ 110°C

Post-exposure bake

Typical PEB parameters:

- PEB temperature: 110°C

- PEB time: 60 s

The recommended PEB for nLOF is 60 seconds at 110°C, regardless of resist film thickness.

PEB baking time investigation

While 60 s @ 110°C is adequate for Si substrates, less thermally conductive substrates (glass, III-V materials, chips bonded to carrier), have shown problems using the standard PEB recipe.

These problems were largely solved by increasing the PEB time to 120 s. Tests (on Aligner: Maskless 02) have shown that the lithographic performance of nLOF on Si is improved when using 120 s @ 110°C PEB (less stitching, less bias, more negative profile).

A small report on the tests can be found here.

Development

Development speed:

- Puddle development in 2.38% TMAH (AZ 726 MIF): ~4 µm/min

A 2 µm nLOF resist film is fully developed in ~30 s in 2.38% TMAH (AZ 726 MIF). However, the development can be continued to 60 s in order to get a more negative resist profile (due to increased under-cut).