Specific Process Knowledge/Lithography/UVExposure: Difference between revisions

| Line 163: | Line 163: | ||

== III-V Aligner == | == III-V Aligner == | ||

'''Feedback to this section''': '''[mailto:labadviser@danchip.dtu.dk?Subject=Feed%20back%20from%20page%20http://labadviser.danchip.dtu.dk/index.php/Specific_Process_Knowledge/Lithography/Coaters#III-V_Aligner click here]''' | |||

The SÜSS MicroTec MA1006 mask aligner located in the III-V cleanroom is dedicated for processing of III-V compound semiconductors. | The SÜSS MicroTec MA1006 mask aligner located in the III-V cleanroom is dedicated for processing of III-V compound semiconductors. | ||

Revision as of 14:24, 3 October 2013

UV Exposure Comparison Table

| Equipment | KS Aligner | EVG Aligner | III-V Aligner | Inclined UV Lamp | |

|---|---|---|---|---|---|

| Purpose |

|

|

|

| |

| Performance | Minimum feature size |

|

|

|

|

| Exposure light/filters/spectrum |

|

|

|

| |

| Exposure mode |

|

|

|

| |

| Process parameter range | Positive Process |

|

|

|

|

| Negative Process |

then 210mW/cm2 flood exposure after PEB |

then 210mW/cm2 flood exposure after PEB |

|

| |

| Substrates | Batch size |

|

|

|

|

| Allowed materials |

|

|

|

| |

KS Aligner

Feedback to this section: click here

SUSS Mask Aligner MA6 is designed for high resolution photolithography.

The 365nm exposure wavelength version is capable of 1.25 (1.0) um resolution in vacuum contact. All contact exposure programs (vacuum, hard, soft, proximity) are supplied.

Two alignment options are available: top side alignment (TSA) with a split field or a video microscope and back side alignment (BSA) with BSA microscope. It is also possible to make IR- light alignment.

The user manual(s), quality control procedure(s) and results and contact information can be found in LabManager: Equipment info in LabManager

EVG Aligner

Feedback to this section: click here

EVG620 aligner is designed for high resolution photolithography. The machine can be used for 2, 4 and 6 inch substrates. Cassette-to-cassette handling option is available only for 6inch substrates. The automatic pattern recognition software is available for the special alignment marks design recommended of EVGroup. Please contact Danchip staff for further information. Available exposure mode: proximity, soft, hard and vacuum contact. Two alignment options are available: top side alignment (TSA) and back side alignment (BSA). IR-light alignment also an option.

The user manual(s), quality control procedure(s) and results and contact information can be found in LabManager: Equipment info in LabManager

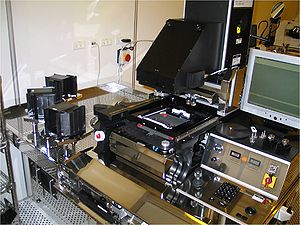

III-V Aligner

Feedback to this section: click here

The SÜSS MicroTec MA1006 mask aligner located in the III-V cleanroom is dedicated for processing of III-V compound semiconductors.

Specific use of the mask aligner can be found in the standard resist recipes.

| Performance | substrate size |

small pieces 1x1 cm up to 2inch" |

|---|---|---|

| Exposure mode |

soft contact, hard contact, proximity, flood exposure | |

| Exposure light/filters |

365 nm, 405 nm | |

| Minimum structure size |

~1µm | |

| Mask size |

5x5inch | |

| Alignment modes |

Top side only |

Inclined UV Lamp

The Inclined UV lamp is 1000 W Hg(Xe)lamp source designed for near UV, 350-450nm, mid UV, 260-320nm, and deep UV, 220-260nm exposures of resists and polymers. The exposure source can be also used to make an inclined exposure in air or in the media tank.

The tool was purchased in February 2009 from Newport. The exposure lamp has a official name: Oriel Flood Exposure Source, unit 92540. All other parts of equipment: substrate and mask holder with media tank, exhaust box around the tool, timer controller, were designed and build at DTU Danchip workshop.

The substrate and mask holder with a media tank was designed as part of Master Thesis of DTU Nanotech, Andres Kristensen group. The exhaust box was made as part of safety and the timer controller was build to control exposure time.

The technical specification and the general outline of the equipment can be found in LabManager.

The user manual(s), quality control procedure(s) and results and contact information can be found in LabManager: Equipment info in LabManager