Specific Process Knowledge/Lithography/EBeamLithography: Difference between revisions

No edit summary |

|||

| Line 10: | Line 10: | ||

!colspan="2" border="none" style="background:silver; color:black;" align="center"|Equipment | !colspan="2" border="none" style="background:silver; color:black;" align="center"|Equipment | ||

|style="background:silver; color:black;" align="left"| | |style="background:silver; color:black;" align="left"|[[Specific_Process_Knowledge/Lithography/EBeamLithography/JEOL_JBX-9500FSZ|JEOL JBX-9500FSZ]] | ||

|style="background:silver; color:black;" align="left"|'''Raith Elphy''' | |style="background:silver; color:black;" align="left"|'''Raith Elphy''' | ||

|- | |- | ||

Revision as of 12:14, 28 January 2016

Feedback to this page: click here

Performance of the e-beam writers at DTU Danchip

| Equipment | JEOL JBX-9500FSZ | Raith Elphy | |

|---|---|---|---|

| Performance | Resolution | ~5 nm beam diameter, ~10 nm lines obtained in 50 nm thick resist (CSAR) | |

| Maximum writing area without stitching | 1mm x 1mm | ||

| Process parameter range | E-beam voltage | 100 kV | 5-25 kV |

| Scanning speed | 100 MHz | ? MHz | |

| Min. electron beam size | 4 nm | ||

| Min. step size | 1 nm | 1 nm | |

| Beam current range | 0.1nA to 60nA in normal conditions | X-Y nA | |

| Dose range | 0.001 - 100000µC/cm2 | µC/cm2 | |

| Samples | Batch size |

Wafer cassettes:

|

|

| Substrate material allowed |

|

| |

E-beam resists and Process Flows

The table describes the e-beam resist used in the cleanroom for standard e-beam exposure. Some of resists are not provided by DTU Danchip and some are not yet approved for common use in the cleanroom and are currently being tested. If you wish to test some of these resists or other resists, please contact Lithography.

Standard DTU Danchip resists purchased and tested by DTU Danchip:

| Resist | Polarity | Manufacturer | Comments | Technical reports | Spin Coater | Thinner | Developer | Rinse | Remover | Process flows (in docx-format) |

| CSAR | Positive | AllResist | Standard positive resist, very similar to ZEP520. | Allresist_CSAR62_English.pdf,, CSAR_62_Abstract_Allresist.pdf | See table here | Anisole | AR-600-546, AR-600-548, N50, MIBK:IPA | IPA | AR-600-71, 1165 Remover | Process Flow CSAR.docx Process Flow CSAR with ESPACER Process Flow CSAR with Al |

| ZEP520A | Positive resist, contact Lithography if you plan to use this resist | ZEON | Positive resist | ZEP520A.pdf, ZEP520A spin curves on SSE Spinner | See table here | Anisole | ZED-N50/Hexyl Acetate,n-amyl acetate, oxylene. JJAP-51-06FC05.pdf, JVB001037.pdf | IPA | acetone/1165 | Process_Flow_ZEP.docx

|

| Copolymer AR-P 617 | Positive | AllResist | Approved, not tested yet. Used for trilayer (PEC-free) resist-stack or double-layer lift-off resist stack. Please contact Lithography for information. | AR_P617.pdf | See table here | PGME | AR 600-55, MIBK:IPA | acetone/1165 | Trilayer stack: Process_Flow_Trilayer_Ebeam_Resist.docx | |

| mr EBL 6000.1 | Negative | MicroResist | Standard negative resist | mrEBL6000 processing Guidelines.pdf | See table here | Anisole | mr DEV | IPA | mr REM | Process_Flow_mrEBL6000.docx

|

| HSQ (XR-1541) | Negative | DOW Corning | Approved. Standard negative resist, mainly for III-V materials | See table here | TMAH, AZ400K:H2O | H2O | ||||

| AR-N 7520 | Negative | AllResist | Both e-beam, DUV and UV-sensitive resist. Currently being tested, contact Peixiong Shi for information. | AR-N7500-7520.pdf | See table here | PGMEA | AR 300-47, TMAH | H2O |

|

Non-standard DTU Danchip resists not purchased by DTU Danchip:

| Resist | Polarity | Manufacturer | Comments | Technical reports | Spinner | Thinner | Developer | Rinse | Remover | Process flows (in docx-format) |

| PMMA | Positive | AllResist | We have various types of PMMA in the cleanroom. Please contact Lithography for information. | See table here | Anisole | MIBK:IPA (1:3), IPA:H2O | IPA | acetone/1165/Pirahna |

| |

| ZEP7000 | Positive | ZEON | Not approved. Low dose to clear, can be used for trilayer (PEC-free) resist-stack. Please contact Lithography for information. | ZEP7000.pdf | See table here | Anisole | ZED-500/Hexyl Acetate,n-amyl acetate, oxylene. | IPA | acetone/1165 | Trilayer stack: Process_Flow_Trilayer_Ebeam_Resist.docx |

Proximity Error Correction

Even though the electron beam diameter is below 5 nm, the feature and pitch resolution in resist is limited by the forward and backward scattering of the electrons. The forward scattering depends on the electron acceleration voltage, the resist material and thickness. The backward scattering depends on the electron acceleration voltage and the substrate material [1], [2].

As the travel distance of backscattered electrons is fairly large, e-beam patterned structures will be influenced by adjacent e-beam patterned structures, i.e. a proximity effect. These proximity effects can be avoided either by simulating a proximity error correction (PEC) in BEAMER or by using the right stack of e-beam resist.

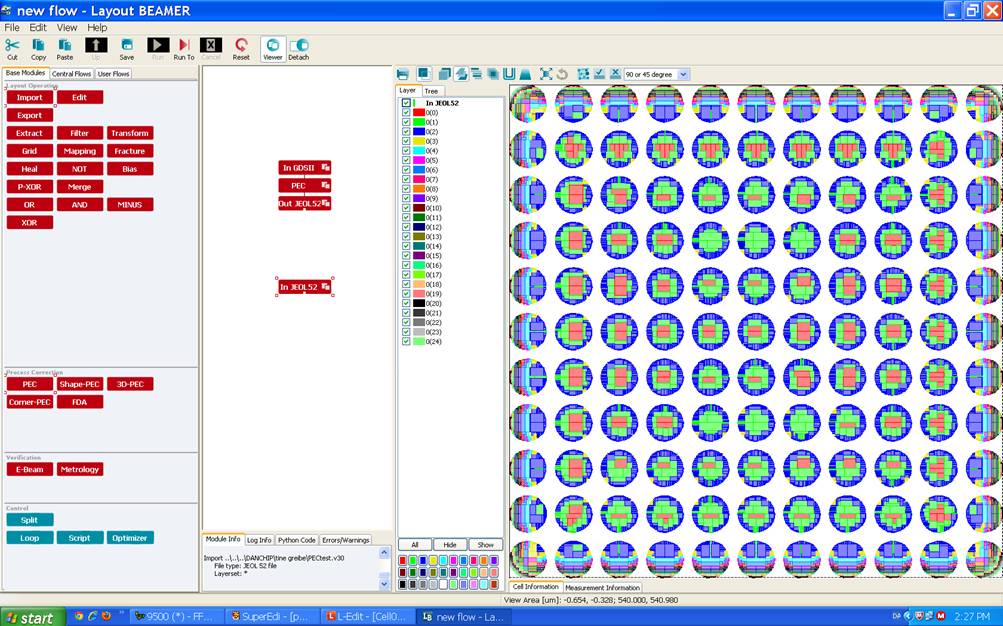

Proximity Error Correction (PEC) in BEAMER

BEAMER is endowed with a software that corrects for proximity errors in the e-beam exposure. You can read more about this function in the BEAMER manual here and in the BEAMER presentation here BEAMERPresentation.pdf.

The proximity error correction require a forward and a backward range parameter, alfa and beta, and a ratio of backscattered energy to the forward scattered energy, eta. As alfa depends on the electron acceleration voltage, which is constant at 100kV, alfa is in BEAMER fixed to 0.007. Help to find beta and eta can be found here.

Alternatively, a point-spread function can be used in BEAMER to calculate the optimised dose-variation.

Trilayer resist stack

As an alternative to PEC, a trilayer reists stack with a thin layer of thermally evaporated Ge can be used [3]. This reists stack has not yet been tested at DTU Danchip. A process flow for this procedure can be found here Process_Flow_Trilayer_Ebeam_Resist.docx, but please contact Lithography before use.

Charging of non-conductive substrates

All substrates are grounded to the cassette when properly loaded. In a non-conducting substrate, the accumulation of charges in the substrates will however destroy the e-beam patterning. To avoid this, a charge dissipating layer is added on top of the e-beam resist; this will provide a conducting layer for the electrons to escape, while high-energy electrons will pass through the layer to expose the resist.

If you wish to investigate the charge dissipation using other methods than below, please contact Lithography.

ESPACER

Espacer is a chemical that works as a discharging layer; it is spun onto the wafer on top of the resist and easily rinsed off the wafer after e-beam exposure. Visit this page for more information: Espacer

Aluminum coating

At DTU Danchip, we recommend to use a thin (20 nm) layer of thermally evaporated aluminum on top of the e-beam resist. Preferably, the thickness of Al and the e-beam dose should be optimised to the features you wish to e-beam pattern [4]. A good starting point is 20 nm Al; from here dose and development can be optimised to reach the resolution and feature size required.

The process flow for a standard e-beam exposure on CSAR with Al on top can be found here Process Flow CSAR with Al.