Specific Process Knowledge/Etch/AOE (Advanced Oxide Etch)/Quartz etch using AOE

Appearance

Nanoetch in quartz 65mmx65mmx6.25mm substrates

by bge@danchip

Some priliminary results

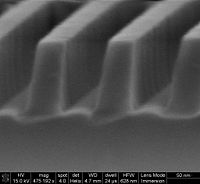

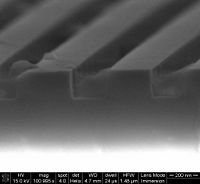

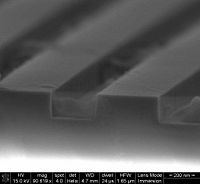

The tests were done on 2" quartz wafers with a thickness of 1mm. These were placed on a 65mmx65mmx6,25mm quartz plate with a 2" groove. This 65mmx65mmx6,25mm plate was placed on a 4" Si wafer with a 65mmx65mm groove. the masking material was Cr sputter deposited in Wordentec and and patterned with ZEP520A resist by e-beam and ICP metal Cr etch.

Recipe used STS65x65:

| Parameter | Crom mask |

|---|---|

| Coil Power [W] | 1200 |

| Platen Power [W] | 500 |

| Platen temperature [oC] | 50 |

| CF flow [sccm] | 43 |

| CF flow [sccm] | 20 |

| O flow [sccm] | 10 |

| Pressure [mTorr] | 8 |

| Parameter | Results |

|---|---|

| Etch rate | ~300nm/min |

| Etch profile | 86-87 degrees |

| ARDE | There does not seem to be a significant aspect ratio dependency in the etch rate up to aspect ratio 1:2 ~ 1:3 |

| Mask selectivity | 20nm Cr is enough to etch 200nm in the quartz |

| Images | . |