Specific Process Knowledge/Lithography/EBeamLithography/JEOLPatternPreparation: Difference between revisions

| Line 24: | Line 24: | ||

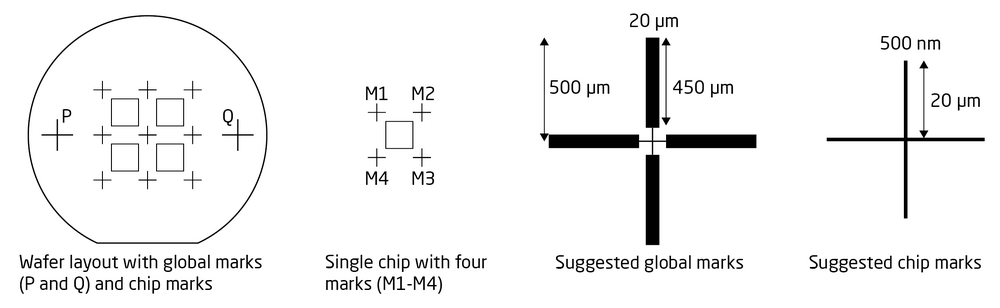

=== Alignment mark position and dimensions === | === Alignment mark position and dimensions === | ||

As a minimum two global alignment marks must be present on the substrate for alignment. In JEOL terms these are P and Q marks. These can be used to align a full substrate design or as initial alignment of chip arrays with individual chip marks. For chip alignment either one mark (M1) or four marks (M1-M4) must be used. | As a minimum two global alignment marks must be present on the substrate for alignment. In JEOL terms these are P and Q marks. These can be used to align a full substrate design or as initial alignment of chip arrays with individual chip marks. For chip alignment either one mark (M1) or four marks (M1-M4) must be used. Global alignment (SETWFR) has a rough scan and a fine scan condition. | ||

[[File:9500AlignmentMarks.png|1000px|center|frameless]] | [[File:9500AlignmentMarks.png|1000px|center|frameless]] | ||

Revision as of 17:10, 30 January 2023

Feedback to this page: click here

Pattern preparation for exposure on JEOL 9500

Prior to exposure a pattern must be prepared for exposure. The original pattern must be provided in GDS format. Depending on requirements and complexity level pattern preparation will involve all or subset of the following steps.

- Alignment preparation

- Bulk and sleeve separation

- Proximity Effect Correction

- Pattern fracturing

- Field sorting

- Export for writing

Alignment preparation

Detection of alignment mark

If an exposure is first print on the substrate and there is no further EBL steps on the substrate, i.e. no EBL alignment, this step can be skipped.

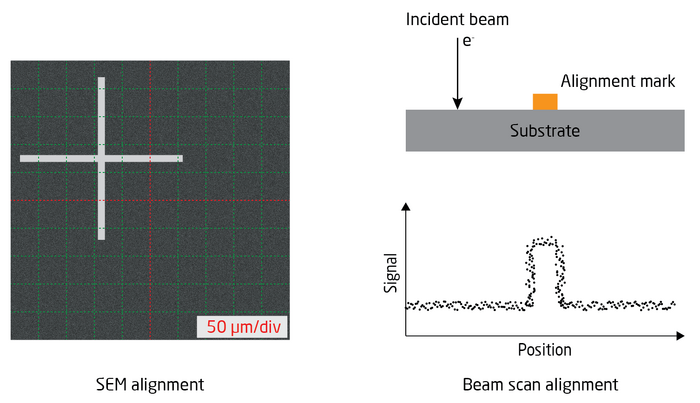

If alignment is needed it is vital to consider this already at the process design and mask design level to ensure that a visible mark is produced. Alignment is done using the electron beam in either SEM mode or beam scan mode. In SEM mode the stage is moved to the expected alignment mark position and the user will manually observe the SEM image and adjust stage position to center the mark at as high magnification as required by alignment tolerance of the design. In beam scan mode the user sets up a routine that will scan the beam across the expected mark position and the Backscatter Electron Detector (BED) will detect the backscattered signal. This is done in both x- and y-directions and system will calculate the mark center based on this.

The advantage of SEM mode is that it is fairly straight forward to do. It is however also very slow as it requires constant user input to move the stage at higher and higher magnification levels until position is sufficiently determined. Due to the time it takes it is hardly realistic to do chip alignment, only global wafer alignment should be done in this way.

Automatic alignment by beam scan is significantly faster, it only takes a couple of seconds per scan. Hence this is the only realistic way of doing chip alignment. It can however be challenging to get sufficient signal on the BED for this to work if this has not already been thought into the mask and process design. Bear in mind that the electron beam is 100 kV and unless there is a relatively high difference in atomic mass between mark and substrate the signal or contrast between substrate and mark will be too low. Gold marks on Si substrates will usually work great. Deep and narrow features etched into a substrate will also work fine. Please consult with the E-beam staff or experienced colleagues when making your mark design.

Alignment mark position and dimensions

As a minimum two global alignment marks must be present on the substrate for alignment. In JEOL terms these are P and Q marks. These can be used to align a full substrate design or as initial alignment of chip arrays with individual chip marks. For chip alignment either one mark (M1) or four marks (M1-M4) must be used. Global alignment (SETWFR) has a rough scan and a fine scan condition.