Specific Process Knowledge/Thermal Process/RTP Annealsys: Difference between revisions

| Line 81: | Line 81: | ||

==Previous work on RTP Annealsys== | ==Previous work on RTP Annealsys== | ||

===General Description=== | ===General Description=== | ||

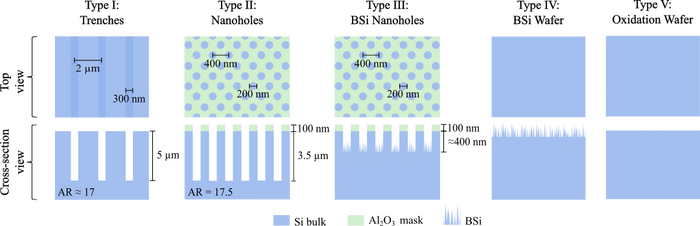

[[File:Test samples.png|700px|thumb|right|Schematic representation of the different types of test samples. The drawing is not to scale. The depth in Type III samples varies between 300 nm and 400 nm. The native silicon oxide on Type V samples was stripped before processing, using a BHF with surfactant bath (12% HF with ammonium fluoride etching mixture).]] | |||

====Experiments Overview==== | ====Experiments Overview==== | ||

Considering the available process gases, various types of RTP were studied, such as rapid thermal annealing '''(RTA)''', hydrogenation '''(RTH)''', oxidation '''(RTO)''', vacuum '''(RTV)''' and Black Si smoothing '''(Clean BSi)'''. In addition, it was developed a sequence for tool calibration. | Considering the available process gases, various types of RTP were studied, such as rapid thermal annealing '''(RTA)''', hydrogenation '''(RTH)''', oxidation '''(RTO)''', vacuum '''(RTV)''' and Black Si smoothing '''(Clean BSi)'''. In addition, it was developed a sequence for tool calibration. | ||

====Test Samples==== | ====Test Samples==== | ||

Various test samples were used, which are represented on the right. Type I, II and III samples are 1 cm x 1 cm chips. Type IV and V are 150 mm Si <100> n-type wafers, with grown BSi and without native oxide, respectively. | Various test samples were used, which are represented on the right. Type I, II and III samples are 1 cm x 1 cm chips. Type IV and V are 150 mm Si <100> n-type wafers, with grown BSi and without native oxide, respectively. | ||

Revision as of 11:41, 30 January 2023

THIS PAGE IS UNDER CONSTRUCTION

RTP Annealsys - Rapid Thermal Processor

January 2023: The RTP Annealsys is being tested, but it is not released for general use yet. Please contact thinfilm@nanolab.dtu.dk for more information.

RTP Annealsys (RTP AS-Premium, serial number AS0415C4 - 7484, from ANNEALSYS) is a research tool available at DTU Nanolab that can reach very high temperatures in a matter of a few minutes or even seconds. Therefore, it is able to perform several types of rapid thermal processing and it can be used as a multi-functional and versatile microfabrication tool, within specific process windows for each process type, using Si/nanofabricated Si structures. Currently, it is used for rapid thermal annealing and smoothing of silicon bases samples.

The Set-Up

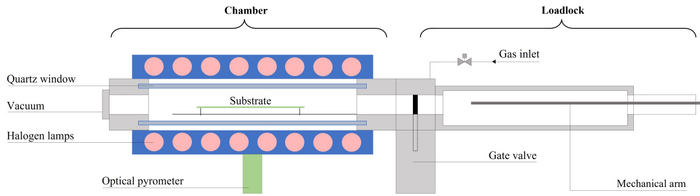

The RTP Annealsys system is divided into two main parts: the process chamber and the loadlock.

The chamber has stainless steel walls (water-cooled) and a top and bottom halogen lamp-configuration (16 infra-red lamps, in total). As such, the samples are rapidly heated from both sides, simultaneously. In addition, the chamber is enclosed by two quartz-windows (immediately below/above the set of top/bottom lamps) and these are air-cooled. It is also connected to two external vacuum pumps, to a gas inlet and the loadlock.

Similarly, the loadlock is also connected to two external pumps. Moreover, the chamber and the loadlock are separated by the gate valve. While processing, the valve remains closed; it is only opened to exchange the substrates when both chamber and loadlock are under turbo vacuum. The substrate transfer is possible due to the mechanical, retractable arm.

Temperature Measurement and Control

RTP Annealsys offers an optical pyrometry system for temperature measurement, not requiring any contact with the wafer.

Regarding setting the process temperature, it is also important to mention the tool can function under two distinct modes – power and temperature/pyro control modes. In other words, using power control mode, the tool is programmed to fix the lamp’s power at a specific value (%) and consequently, the temperature inside the chamber varies with time; using the temperature/pyro control mode, the tool is programmed to vary the lamps’ power to maintain the temperature stable and constant inside the chamber at a previously established value in the recipe.

Samples and Process Specifications

The RTP Annealsys, with a base pressure of 10-6 mbar, is a research tool. As such, there are some parameters and details to consider.

| Specifics | Allowed | |

|---|---|---|

| Temperature |

| |

| Process gas | Ar |

|

| O2 |

| |

| NH3 |

| |

| 5% H2/Ar |

| |

| Pressure | Valve (APC) |

|

| Controller |

| |

| Substrates | Batch size |

|

| Substrate size |

| |

| Allowed materials |

| |

Previous work on RTP Annealsys

General Description

Experiments Overview

Considering the available process gases, various types of RTP were studied, such as rapid thermal annealing (RTA), hydrogenation (RTH), oxidation (RTO), vacuum (RTV) and Black Si smoothing (Clean BSi). In addition, it was developed a sequence for tool calibration.

Test Samples

Various test samples were used, which are represented on the right. Type I, II and III samples are 1 cm x 1 cm chips. Type IV and V are 150 mm Si <100> n-type wafers, with grown BSi and without native oxide, respectively.

Type of characterization

The structural characterization was mainly carried out by scanning electron microscopy, although ellipsometry has also been used. The scanning electron microscope (SEM) was a Zeiss Supra 40VP SEM, serial number 4825 and the ellipsometer a variable angle spectroscopic ellipsometry (VASE) M2000XI-210 from J.A. Woollam Co., Inc.

Processes in detail

Argon RTA

Rapid thermal annealing sequences were developed and studied using only argon (Ar). Some experiments were repeated in an attempt to establish a reproducibility study. Type I samples were used and processed on top of silicon carrier wafers, with no bonding required. The details for each experiment are presented in the following table.

RTH

Hydrogen/Argon RTA

Clean BSi

RTO

RTV

Tool Calibration

Feedback to this page: click here