Specific Process Knowledge/Etch/ICP Metal Etcher/silicon oxide: Difference between revisions

Appearance

No edit summary |

No edit summary |

||

| Line 1: | Line 1: | ||

'''Feedback to this page''': '''[mailto:labadviser@danchip.dtu.dk?Subject=Feed%20back%20from%20page%20http://labadviser.danchip.dtu.dk/index.php/Specific_Process_Knowledge/Etch/ICP_Metal_Etcher/silicon_oxide click here]''' | |||

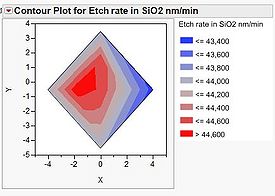

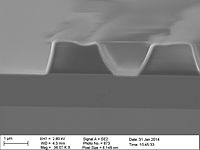

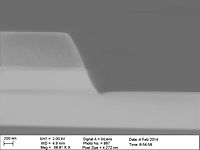

===Slow etch of SiO2 with resist as masking material - using a 6" carrier wafer with recess === | ===Slow etch of SiO2 with resist as masking material - using a 6" carrier wafer with recess === | ||

This recipe can be used for slow etching of SiO2 with resist as masking material. Here are some test results presented. | This recipe can be used for slow etching of SiO2 with resist as masking material. Here are some test results presented. | ||

Revision as of 09:27, 21 February 2014

Feedback to this page: click here

Slow etch of SiO2 with resist as masking material - using a 6" carrier wafer with recess

This recipe can be used for slow etching of SiO2 with resist as masking material. Here are some test results presented.

| Parameter | Resist mask |

|---|---|

| Coil Power [W] | 200 |

| Platen Power [W] | 25 |

| Platen temperature [oC] | 0 |

| CF4 flow [sccm] | 20 |

| H2 flow [sccm] | 10 |

| Pressure [mTorr] | 3 |