Specific Process Knowledge/Etch/IBE⁄IBSD Ionfab 300/IBE Si etch: Difference between revisions

No edit summary |

|||

| (One intermediate revision by the same user not shown) | |||

| Line 3: | Line 3: | ||

=Results for Si etching in the IBE= | =Results for Si etching in the IBE= | ||

''Made by Kristian Hagsted Rasmussen | ''Made by Kristian Hagsted Rasmussen. DTU Nanotech in 2011'' <br> | ||

The silicon etch test was made as a preliminary test of the IBE system, to obtain a feeling of the system capabilities and the different parameters influence on the etch outcome. A throughout characterization of the wafers was not carried out. However, the most important results are listed here. | The silicon etch test was made as a preliminary test of the IBE system, to obtain a feeling of the system capabilities and the different parameters influence on the etch outcome. A throughout characterization of the wafers was not carried out. However, the most important results are listed here. | ||

| Line 49: | Line 49: | ||

|- | |- | ||

|Etch rate in Silicon nitride (low stress) | |Etch rate in Silicon nitride (low stress) | ||

|9. | |9.1 nm/min (2013-05-27 BGHE and Matthias F. Carnoy) | ||

|- | |- | ||

|Etch rate DUV resist | |Etch rate DUV resist | ||

|13. | |13.4 nm/min (2013-05-27 BGHE and Matthias F. Carnoy) | ||

|- | |- | ||

|} | |} | ||

| Line 62: | Line 62: | ||

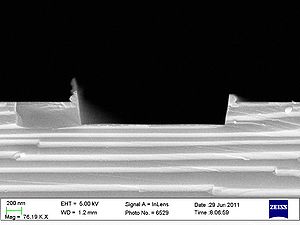

[[image:Silicon-IBE-good-b17.jpg|300x300px|thumb|center|Silicon etch in IBE with good corner definition. Small hare ears are obvious at the structure edge. Substrate etched with Beam current=400mA, Beam voltage=600V, Beam acceleration Voltage=400V, and Stage angle=5°]] | [[image:Silicon-IBE-good-b17.jpg|300x300px|thumb|center|Silicon etch in IBE with good corner definition. Small hare ears are obvious at the structure edge. Substrate etched with Beam current=400mA, Beam voltage=600V, Beam acceleration Voltage=400V, and Stage angle=5°]] | ||

! | ! | ||

[[image:Silicon-IBE-bad-b21.jpg|300x300px|thumb|center|Silicon etch in IBE with rounded corners. Large hare ears with | [[image:Silicon-IBE-bad-b21.jpg|300x300px|thumb|center|Silicon etch in IBE with rounded corners. Large hare ears with rippling's are seen at the structure edge. Substrate etched with Beam current=500mA, Beam voltage=500V, Beam acceleration Voltage=500V, and Stage angle=10°]] | ||

|} | |} | ||

Latest revision as of 11:30, 4 September 2025

Feedback to this page: click here

Results for Si etching in the IBE

Made by Kristian Hagsted Rasmussen. DTU Nanotech in 2011

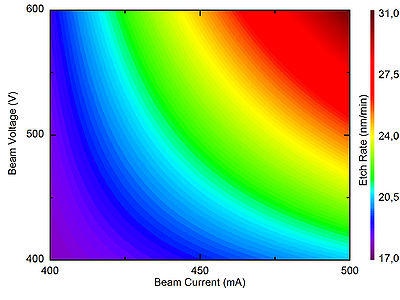

The silicon etch test was made as a preliminary test of the IBE system, to obtain a feeling of the system capabilities and the different parameters influence on the etch outcome. A throughout characterization of the wafers was not carried out. However, the most important results are listed here. The table list the best etch definition obtained. The IBE etcher should only be used for silicon etching, if you have a specific need that cannot be accommodated in a RIE tool. This could be excessive amount of metals on the surface or a layer of silicon in a stack of several layers that all must be etched. The corner definition is strongly dependent on both accelerator and beam voltage and of course the incident angle. However, no interactions between parameters seem to influence the angle outcome. The good corner definition will introduce hare ears at the resist edge. This is best limited by use of thin resist layers slightly thicker than needed to mask for the duration of the etch. Be aware that the selectivity between silicon and resist is poor.

Best recipe with respect to the etch profile and low redeposition

| Parameter | Best Si etching recipe so fare |

|---|---|

| Neutalizer current [mA] | 450 |

| RF Power [W] | 1200 |

| Beam current [mA] | 400 |

| Beam voltage [V] | 600 |

| Beam accelerator voltage | 400 |

| Ar flow to neutralizer [sccm] | 6.0 |

| Ar flow to beam [sccm] | 6.0 |

| Rotation speed [rpm] | 20 |

| Stage angle [degrees] | 5 |

| Results | vvv |

| Etch rate in Si [nm/min] | 17-18 |

| Etch rate in Silicon nitride (low stress) | 9.1 nm/min (2013-05-27 BGHE and Matthias F. Carnoy) |

| Etch rate DUV resist | 13.4 nm/min (2013-05-27 BGHE and Matthias F. Carnoy) |