LabAdviser/Technology Research/Fabrication of Hyperbolic Metamaterials using Atomic Layer Deposition/AZO pillars: Difference between revisions

mNo edit summary |

|||

| (15 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

= | '''Feedback to this page''': '''[mailto:labadviser@nanolab.dtu.dk?Subject=Feed%20back%20from%20page%20http://labadviser.nanolab.dtu.dk/index.php/LabAdviser/Technology_Research/Fabrication_of_Hyperbolic_Metamaterials_using_Atomic_Layer_Deposition/AZO_pillars click here]''' | ||

<i>This page is written by <b>Evgeniy Shkondin @DTU Nanolab</b> if nothing else is stated. <br> | |||

All images and photos on this page belongs to <b>DTU Nanolab</b> and <b>DTU Electro</b> (previous DTU Fotonik).<br></i> | |||

= | =Fabrication of Hyperbolic Metamaterials by ALD: AZO Pillars= | ||

The fabrication and characterization described below were conducted in <b>2013-2016 by Evgeniy Shkondin, DTU Nanolab</b>.<br> | |||

The | |||

== | == Procces flow description == | ||

Double side polished (DSP), 150 mm (100) Si wafers were selected for device fabrication. They were RCA cleaned and later oxidized in a conventional quartz tube (furnace from Tempress) using a dry oxidation process based on O<sub>2</sub> at 1100 °C, resulting in a 200 nm SiO<sub>2</sub> layer on Si. Next, a 2 μm amorphous Si layer was deposited on the SiO<sub>2</sub> surface using a conventional low-pressure chemical vapor deposition (LPCVD) process (furnace from | |||

Tempress) based on SiH<sub>4</sub> at 560 °C. This procedure enables the preparation of home-made silicon-on-insulator (SOI) substrates. | |||

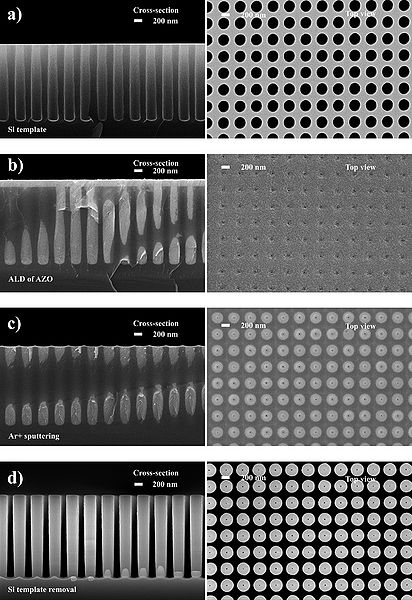

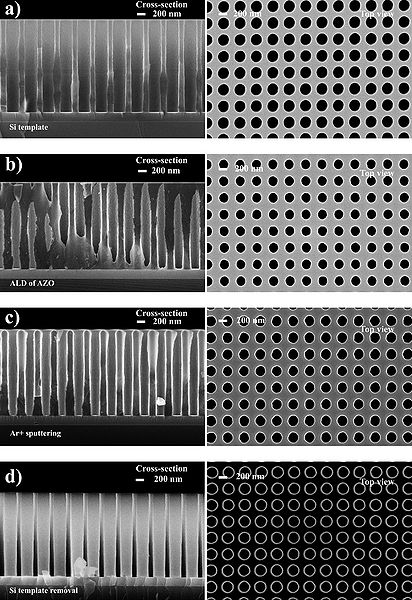

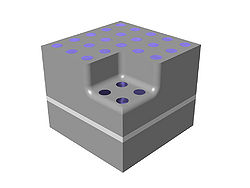

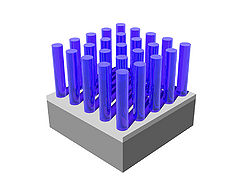

The main steps in the fabrication of pillars and tubes are shown in Fig 1. Initially, silicon holes were etched in SOI wafers by deep-UV lithography and DRIE (Fig. 1(a)-1(c)). The holes were arranged in a square lattice with the pitch of 400 nm. The template was then filled with an ALD D25 AZO coating (Fig. 1(d)) at 250 °C. The thickness of the deposited AZO depends on the desired output. An entire filling would result in the formation of pillars, while partial deposition leads to fabrication of hollow tubes. After removal of the top parts by Ar+ ion sputtering (Fig. 1(e)), the silicon core between the ALD coated holes was etched away during the last step. Figure 1(f) represents the final structures. Fabrication output is shown in Fig. 2. Each process step was carefully analyzed using cross-sectional SEM imaging (see Figs. 3 and 4 for pillars and tubes fabrication, respectively). | |||

<br clear="all" /> | |||

<gallery caption="" widths="500px" heights="600px" perrow=" | <gallery caption="" widths="500px" heights="600px" perrow="2"> | ||

image:Fabrication_shematic_AZO_pillars_eves2.jpg| | image:Fabrication_shematic_AZO_pillars_eves2.jpg|Figure 1. Schematics of the fabrication flow. a) Home-made SOI substrates. b) Deep-UV lithography. Resist spin coating, baking, exposure and developing. c) DRIE etching, fabrication of initial Si template. d) ALD deposition of D25 AZO at 250 °C. Partial deposition will lead to fabrication of tubes, while complete filling will create full pillars. e) Removal of the top AZO layer by Ar+ sputtering. f) Silicon host removal using conventional RIE process. | ||

image:AZO_structures_fab_supplementary_eves.jpg|Figure 2. SEM images, bird-eye-view. a) AZO pillars, and b) AZO tubes. | |||

</gallery> | </gallery> | ||

<br clear="all" /> | <br clear="all" /> | ||

<gallery caption="" widths="500px" heights="600px" perrow=" | <gallery caption="" widths="500px" heights="600px" perrow="2"> | ||

image:AZO_pillars_fab_supplementary_eves.jpg| | image:AZO_pillars_fab_supplementary_eves.jpg| Figure 3. SEM verification for each fabrication step of pillars production. Substrate is normal Si-wafer. Left side shows cross-sectional images and right side of the Figure shows the top view of the structures. | ||

image:AZO_tubes_fab_supplementary_eves.jpg| | image:AZO_tubes_fab_supplementary_eves.jpg| Figure 4. SEM verfication for each fabrication step of tube production. Substrate is silicon-on-isolator (SOI). Left side shows cross-sectional images and right side of the Figure shows the top view of the structures. | ||

</gallery> | </gallery> | ||

== Process flow == | |||

Description of steps for fabrication of AZO nanopillars and tubes. | |||

{| border="1" cellspacing="1" cellpadding="3" style="text-align: left; width: 925px; height: 220px;" | |||

|- | |||

|- | |||

!colspan="2" border="none" style="background:#6495ED; color:black;" align="center" width="225px"|Step | |||

!width="250px" style="background:#6495ED; color:black"|Description | |||

!width="200px" style="background:#6495ED; color:black"|LabAdviser link | |||

!width="260px" style="background:#6495ED; color:black"|Image showing the step | |||

|- | |||

|- | |||

!1.1 | |||

|RCA.(Optional step. Needs only if SOI substrates requires) | |||

|To ensure a clean surface before furnace processing, the wafers needs to be RCA cleaned. | |||

| | |||

[[Specific_Process_Knowledge/Wafer_cleaning/RCA| RCA]] | |||

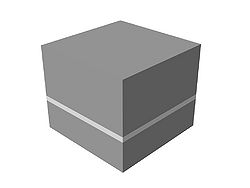

|[[image:1_zero1.jpg|250x350px|center|]] | |||

|- | |||

|- | |||

|- style="background:#BCD4E6; color:black" | |||

!1.2 | |||

|Thermal oxidation of Si.(Optional step. Needs only if SOI substrates requires) | |||

|Creating 200 nm thin SiO2 layer using [[Specific_Process_Knowledge/Thermal Process/Oxidation|Dry Oxidation process]] in a C1 Furnace Anneal-oxide equipment. | |||

|[[Specific_Process_Knowledge/Thermal_Process/C1_Furnace_Anneal-oxide|C1 Furnace Anneal-oxide]]. | |||

|[[image:2_zero2.jpg|250x350px|center|]] | |||

|- | |||

|- | |||

!1.3 | |||

|LPCVD deposition of Si. (Optional step. Needs only if SOI substrates requires) | |||

|LPCVD of amorphous silicon using [[Specific Process Knowledge/Thin film deposition/Furnace LPCVD PolySilicon/Standard recipes, QC limits and results for the 6" polysilicon furnace|AMORPOLY]] recipe in 6" Furnace LPCVD PolySilicon. | |||

|[[Specific Process Knowledge/Thin film deposition/Furnace LPCVD PolySilicon| 6" Furnace LPCVD PolySilicon]]. | |||

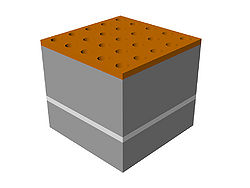

|[[image:3_1_SOI.jpg|250x350px|center|]] | |||

|- | |||

|- | |||

|- style="background:#BCD4E6; color:black" | |||

!1.4 | |||

|DUV Resist patterning. | |||

|DUV | |||

|[[Specific_Process_Knowledge/Lithography/DUVStepperLithography|DUV Stepper Lithography]]. | |||

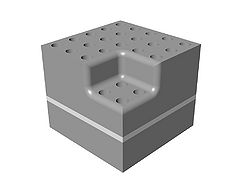

|[[image:4_1_SOI_DUV.jpg|250x350px|center|]] | |||

|- | |||

|- | |||

!1.5 | |||

|Deep reactive ion etching (DRIE). | |||

|DRIE; [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/DUVetch|Recipe: PolySOI10]] Recipe needs to be tuned. Adjusted parameters: temperature, etching and passivation times. | |||

| [[Specific_Process_Knowledge/Etch/DRIE-Pegasus|DRIE Pegasus]]. | |||

|[[image:5_2_DRIE.jpg|250x350px|center|]] | |||

|- | |||

|- | |||

|- style="background:#BCD4E6; color:black" | |||

!1.6 | |||

|Plasma surface treatment. | |||

|To ensure that remainings of DUV resist are gone, samples are treated by O<sub>2</sub>/N<sub>2</sub> plasma. (Optional step) | |||

| | |||

[[Specific_Process_Knowledge/Lithography/Strip#Plasma_Asher_2| Plasma Asher 2]] | |||

<br clear="all" /> | |||

[[Specific_Process_Knowledge/Lithography/Strip#Plasma_asher| Plasma Asher 1]] | |||

<br clear="all" /> | |||

| | |||

|- | |||

|- | |||

!1.7 | |||

|Scanning Electron Microscopy inspection. | |||

|By cleaving the sample it is possible to inspect DRIE etched Si holes in cross-sectional mode. | |||

| | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_1|SEM Supra 1]] | |||

<br clear="all" /> | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_2|SEM Supra 2]] | |||

<br clear="all" /> | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_3|SEM Supra 3]] | |||

|See Figures 3a and 4a above. | |||

|- | |||

|- | |||

|- style="background:#BCD4E6; color:black" | |||

!1.8 | |||

|Atomic Layer Deposition of Al-doped ZnO (AZO). | |||

|Deposition carried at 250<sup>o</sup>C. For compleate pillars the thickness needs to above 100 nm. For AZO tubes only 20 nm (partial deposition) requires. | |||

||Equipment used: [[Specific_Process_Knowledge/Thin_film_deposition/ALD_Picosun_R200|ALD Picosun R200]]. Standard recipe used: [[Specific_Process_Knowledge/Thin_film_deposition/ALD_Picosun_R200/AZO_deposition_using_ALD| AZO 25T]]. | |||

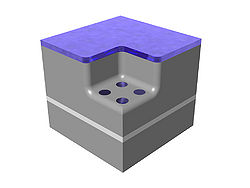

|[[image:6_3_ALD_full pillars.jpg|250x350px|center]] | |||

|- | |||

|- | |||

!1.9 | |||

|Scanning Electron Microscopy inspection. | |||

|By cleaving the sample it is possible to inspect ALD coatings deposited in Si holes in cross-sectional mode. | |||

| | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_1|SEM Supra 1]] | |||

<br clear="all" /> | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_2|SEM Supra 2]] | |||

<br clear="all" /> | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_3|SEM Supra 3]] | |||

|See figures 3b and 4b above. | |||

|- | |||

|- | |||

|- style="background:#BCD4E6; color:black" | |||

!1.10 | |||

|Ion Beam Etching (IBE). | |||

|Opening of deposited AZO top layer using recipe [[Specific_Process_Knowledge/Etch/IBE⁄IBSD_Ionfab_300/IBE_Ti_etch|"Ti acceptance"]] there the stage was placed to 0<sup>o</sup> degree. The back side of the wafer also needs to be exposed to etching. | |||

|[[Specific_Process_Knowledge/Etch/IBE⁄IBSD_Ionfab_300|IBE/IBSD Ionfab 300]] | |||

|[[image:7_ALD_fill pillars_Ar.jpg|250x350px|center]] | |||

|- | |||

|- | |||

!1.11 | |||

|Scanning Electron Microscopy inspection. | |||

|By cleaving the sample it is possible to inspect IBE etching results in cross-sectional mode. | |||

| | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_1|SEM Supra 1]] | |||

<br clear="all" /> | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_2|SEM Supra 2]] | |||

<br clear="all" /> | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_3|SEM Supra 3]] | |||

|See Figures 3c and 4c above. | |||

|- | |||

|- | |||

|- style="background:#BCD4E6; color:black" | |||

!1.12 | |||

|Selective etch of Si between ALD AZO coatings. | |||

|Si etching proceeds using reactive ion etching with isotropic process based on SF<sub>6</sub> process gas. | |||

||Equipment used: [[Specific_Process_Knowledge/Etch/RIE_(Reactive_Ion_Etch)|RIE2]]. | |||

|[[image:8_final pillars.jpg|250x350px|center]] | |||

|- | |||

|- | |||

!1.13 | |||

|Scanning Electron Microscopy inspection of fabricated structures. | |||

|Proof of final result. | |||

| | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_1|SEM Supra 1]] | |||

<br clear="all" /> | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_2|SEM Supra 2]] | |||

<br clear="all" /> | |||

[[Specific_Process_Knowledge/Characterization/SEM_Supra_3|SEM Supra 3]] | |||

|See Figures 2, 3d and 4d above. | |||

|- | |||

|- | |||

|} | |||

<br clear="all" /> | |||

Latest revision as of 21:08, 20 June 2025

Feedback to this page: click here

This page is written by Evgeniy Shkondin @DTU Nanolab if nothing else is stated.

All images and photos on this page belongs to DTU Nanolab and DTU Electro (previous DTU Fotonik).

Fabrication of Hyperbolic Metamaterials by ALD: AZO Pillars

The fabrication and characterization described below were conducted in 2013-2016 by Evgeniy Shkondin, DTU Nanolab.

Procces flow description

Double side polished (DSP), 150 mm (100) Si wafers were selected for device fabrication. They were RCA cleaned and later oxidized in a conventional quartz tube (furnace from Tempress) using a dry oxidation process based on O2 at 1100 °C, resulting in a 200 nm SiO2 layer on Si. Next, a 2 μm amorphous Si layer was deposited on the SiO2 surface using a conventional low-pressure chemical vapor deposition (LPCVD) process (furnace from Tempress) based on SiH4 at 560 °C. This procedure enables the preparation of home-made silicon-on-insulator (SOI) substrates.

The main steps in the fabrication of pillars and tubes are shown in Fig 1. Initially, silicon holes were etched in SOI wafers by deep-UV lithography and DRIE (Fig. 1(a)-1(c)). The holes were arranged in a square lattice with the pitch of 400 nm. The template was then filled with an ALD D25 AZO coating (Fig. 1(d)) at 250 °C. The thickness of the deposited AZO depends on the desired output. An entire filling would result in the formation of pillars, while partial deposition leads to fabrication of hollow tubes. After removal of the top parts by Ar+ ion sputtering (Fig. 1(e)), the silicon core between the ALD coated holes was etched away during the last step. Figure 1(f) represents the final structures. Fabrication output is shown in Fig. 2. Each process step was carefully analyzed using cross-sectional SEM imaging (see Figs. 3 and 4 for pillars and tubes fabrication, respectively).

-

Figure 1. Schematics of the fabrication flow. a) Home-made SOI substrates. b) Deep-UV lithography. Resist spin coating, baking, exposure and developing. c) DRIE etching, fabrication of initial Si template. d) ALD deposition of D25 AZO at 250 °C. Partial deposition will lead to fabrication of tubes, while complete filling will create full pillars. e) Removal of the top AZO layer by Ar+ sputtering. f) Silicon host removal using conventional RIE process.

-

Figure 2. SEM images, bird-eye-view. a) AZO pillars, and b) AZO tubes.

-

Figure 3. SEM verification for each fabrication step of pillars production. Substrate is normal Si-wafer. Left side shows cross-sectional images and right side of the Figure shows the top view of the structures.

-

Figure 4. SEM verfication for each fabrication step of tube production. Substrate is silicon-on-isolator (SOI). Left side shows cross-sectional images and right side of the Figure shows the top view of the structures.

Process flow

Description of steps for fabrication of AZO nanopillars and tubes.

| Step | Description | LabAdviser link | Image showing the step | |

|---|---|---|---|---|

| 1.1 | RCA.(Optional step. Needs only if SOI substrates requires) | To ensure a clean surface before furnace processing, the wafers needs to be RCA cleaned. |  | |

| 1.2 | Thermal oxidation of Si.(Optional step. Needs only if SOI substrates requires) | Creating 200 nm thin SiO2 layer using Dry Oxidation process in a C1 Furnace Anneal-oxide equipment. | C1 Furnace Anneal-oxide. |  |

| 1.3 | LPCVD deposition of Si. (Optional step. Needs only if SOI substrates requires) | LPCVD of amorphous silicon using AMORPOLY recipe in 6" Furnace LPCVD PolySilicon. | 6" Furnace LPCVD PolySilicon. |  |

| 1.4 | DUV Resist patterning. | DUV | DUV Stepper Lithography. |  |

| 1.5 | Deep reactive ion etching (DRIE). | DRIE; Recipe: PolySOI10 Recipe needs to be tuned. Adjusted parameters: temperature, etching and passivation times. | DRIE Pegasus. |  |

| 1.6 | Plasma surface treatment. | To ensure that remainings of DUV resist are gone, samples are treated by O2/N2 plasma. (Optional step) | ||

| 1.7 | Scanning Electron Microscopy inspection. | By cleaving the sample it is possible to inspect DRIE etched Si holes in cross-sectional mode. | See Figures 3a and 4a above. | |

| 1.8 | Atomic Layer Deposition of Al-doped ZnO (AZO). | Deposition carried at 250oC. For compleate pillars the thickness needs to above 100 nm. For AZO tubes only 20 nm (partial deposition) requires. | Equipment used: ALD Picosun R200. Standard recipe used: AZO 25T. |  |

| 1.9 | Scanning Electron Microscopy inspection. | By cleaving the sample it is possible to inspect ALD coatings deposited in Si holes in cross-sectional mode. | See figures 3b and 4b above. | |

| 1.10 | Ion Beam Etching (IBE). | Opening of deposited AZO top layer using recipe "Ti acceptance" there the stage was placed to 0o degree. The back side of the wafer also needs to be exposed to etching. | IBE/IBSD Ionfab 300 |  |

| 1.11 | Scanning Electron Microscopy inspection. | By cleaving the sample it is possible to inspect IBE etching results in cross-sectional mode. | See Figures 3c and 4c above. | |

| 1.12 | Selective etch of Si between ALD AZO coatings. | Si etching proceeds using reactive ion etching with isotropic process based on SF6 process gas. | Equipment used: RIE2. |  |

| 1.13 | Scanning Electron Microscopy inspection of fabricated structures. | Proof of final result. | See Figures 2, 3d and 4d above. | |