Specific Process Knowledge/Etch/DRIE-Pegasus/processC: Difference between revisions

Appearance

No edit summary |

No edit summary |

||

| (8 intermediate revisions by 2 users not shown) | |||

| Line 1: | Line 1: | ||

'''Feedback to this page''': '''[mailto:labadviser@ | '''Feedback to this page''': '''[mailto:labadviser@nanolab.dtu.dk?Subject=Feed%20back%20from%20page%20http://labadviser.nanolab.dtu.dk/index.php/Specific_Process_Knowledge/Etch/DRIE-Pegasus/processC click here]''' | ||

<!--Checked for updates on | <!--Checked for updates on 14/5-2018 - ok/jmli --> | ||

== Process C == | == Process C == | ||

{{contentbydryetch}} | |||

<!--Checked for updates on 2/02-2023 - ok/jmli --> | |||

<!--Checked for updates on 4/9-2025 - ok/jmli --> | |||

Process C is | Process C is intended to be used on features in the sub 2-3 µm range. The recipe was run on a 100 mm Nanolab wafer with a test pattern of a series of lines and dots with sizes ranging from 30 nm to 300 nm. The etch load was extremely high, approaching 100 %. | ||

The 100 mm wafers had an Al mask made by lift-off: | The 100 mm wafers had an Al mask made by lift-off: | ||

# 80 nm of spin coated ZEP520A E-beam resist | # 80 nm of spin coated ZEP520A E-beam resist | ||

# Patterned by E-beam | # Patterned by E-beam lithography | ||

# 20 nm Al deposited and patterned by lift-off | # 20 nm Al deposited and patterned by lift-off | ||

# ~ 99 % etch load | # ~ 99 % etch load | ||

| Line 20: | Line 23: | ||

! Average result | ! Average result | ||

|- | |- | ||

! Etch rate ( | ! Etch rate (nm/min) | ||

| Not specified | | Not specified | ||

| | | | ||

|- | |- | ||

! Etched depth ( | ! Etched depth (nm) | ||

| 300 | | 300 | ||

| | | | ||

| Line 37: | Line 40: | ||

|- | |- | ||

! Selectivity to resist | ! Selectivity to resist | ||

| Not | | Not specified | ||

| | | | ||

|- | |- | ||

| Line 79: | Line 82: | ||

|- | |- | ||

! Common | ! Common | ||

| colspan="4" | Temperature 10 | | colspan="4" | Temperature 10 degsree, HBC 10 torr, long funnel, with baffle & 100 mm spacers | ||

|} | |} | ||

<gallery> | |||

Image:c1 30 nm dots.jpg | |||

Image:c1 50 nm dots 2.jpg | |||

Image:r1 300 nm dots 1.jpg | |||

</gallery> | |||

Latest revision as of 12:01, 4 September 2025

Feedback to this page: click here

Process C

Unless otherwise stated, the content of this page was created by the dry etch group at DTU Nanolab

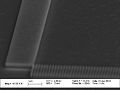

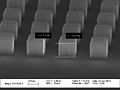

Process C is intended to be used on features in the sub 2-3 µm range. The recipe was run on a 100 mm Nanolab wafer with a test pattern of a series of lines and dots with sizes ranging from 30 nm to 300 nm. The etch load was extremely high, approaching 100 %.

The 100 mm wafers had an Al mask made by lift-off:

- 80 nm of spin coated ZEP520A E-beam resist

- Patterned by E-beam lithography

- 20 nm Al deposited and patterned by lift-off

- ~ 99 % etch load

| Parameter | Specification | Average result |

|---|---|---|

| Etch rate (nm/min) | Not specified | |

| Etched depth (nm) | 300 | |

| Scallop size (nm) | < 30 | |

| Profile (degs) | 85 +/- 5 | |

| Selectivity to resist | Not specified | |

| Undercut (nm) | < 30 | |

| Uniformity (%) | < 3.5 | |

| Repeatability (%) | <4 |

| Parameter | Etch | |||

|---|---|---|---|---|

| Gas flow (sccm) | SF6 38 C4F8 70 | |||

| Process time (mm:ss) | 01:30 | |||

| Pressure (mtorr) | 4 | |||

| Coil power (W) | 450 | |||

| Platen power (W) | 100 | |||

| Common | Temperature 10 degsree, HBC 10 torr, long funnel, with baffle & 100 mm spacers | |||