Specific Process Knowledge/Etch/Etching of Silicon Oxide/SiO2 etch using ASE/Images SiO2RIE

Jump to navigation

Jump to search

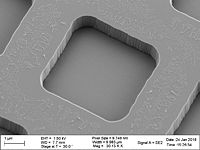

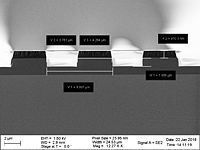

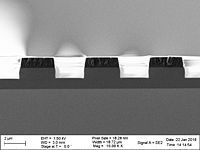

Old SIO2 etch recipe - unstable

SiO2 etch with resist mask on wafer with clamping and He backside cooling

Unless otherwise stated, all content in this section was done by Berit Herstrøm, DTU Nanolab, May 2018

The ASE is now the "dirty" plasma etcher at Nanolab meaning small amount of metals are allowed to be exposed by the plasma. That calls for recipes etching Silicon oxide and silicon nitride as well as silicon in this machine.

Not a lot experiments have been done yet etching SiO2 on wafers that are clamped and cooled but here is the best result so fare.

*This recipe is no longer stable.