Specific Process Knowledge/Etch/DRIE-Pegasus/nanoetch/nano11: Difference between revisions

Appearance

No edit summary |

No edit summary |

||

| (2 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

'''Feedback to this page''': '''[mailto:labadviser@ | '''Feedback to this page''': '''[mailto:labadviser@nanolab.dtu.dk?Subject=Feed%20back%20from%20page%20http://labadviser.nanolab.dtu.dk/index.php/Specific_Process_Knowledge/Etch/DRIE-Pegasus/nanoetch/nano11 click here]''' | ||

<!--Checked for updates on 30/7-2018 - ok/jmli --> | <!--Checked for updates on 30/7-2018 - ok/jmli --> | ||

<!--Checked for updates on 5/10-2020 - ok/jmli --> | |||

<!--Checked for updates on 28/6-2023 - ok/jmli --> | |||

<!--Checked for updates on 4/9-2025 - ok/jmli --> | |||

{{contentbydryetch}} | |||

== The nano1.1 recipe == | == The nano1.1 recipe == | ||

Latest revision as of 12:00, 4 September 2025

Feedback to this page: click here

Unless otherwise stated, the content of this page was created by the dry etch group at DTU Nanolab

The nano1.1 recipe

| Recipe | Gas | C4F8 38 sccm, SF6 52 sccm |

|---|---|---|

| Pressure | 4 mTorr, Strike 3 secs @ 15 mTorr | |

| Power | 600 W CP, 50 W PP | |

| Temperature | 10 degs | |

| Hardware | 100 mm Spacers | |

| Time | 120 secs | |

| Conditions | Run ID | 1815 |

| Conditioning | Sequence: Oxygen clean, MU tests, processes, no oxygen between runs | |

| Mask | 1dfhj10 nm zep etched down to 6dgh4 nm |

- The results of the nano1.1 recipe

-

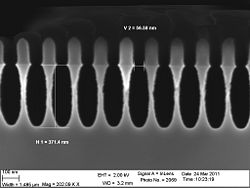

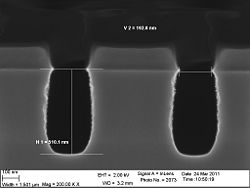

The 30 nm trenches

-

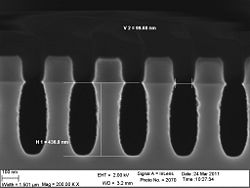

The 60 nm trenches

-

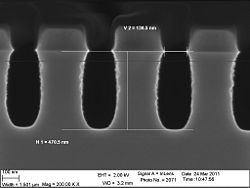

The 90 nm trenches

-

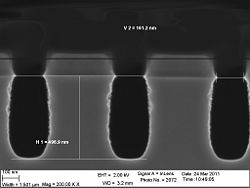

The 120 nm trenches

-

The 150 nm trenches

| Nominal trench line width | ' | 30 | 60 | 90 | 120 | 150 | Avg | Std |

| Etch rates | nm/min | 183 | 218 | 232 | 249 | 256 | 228 | 29 |

| Sidewall angle | degs | 95 | 94 | 94 | 93 | 93 | 94 | 1 |

| Cd loss | nm/edge | -2 | -4 | -16 | -15 | -27 | -13 | 10 |

| CD loss foot | nm/edge | -2 | -4 | -16 | -15 | 3 | -7 | 9 |

| Bowing | 36 | 40 | 49 | 48 | 40 | 42 | 6 | |

| Curvature | -55 | -50 | -39 | -39 | -42 | -45 | 7 | |

| zep | nm/min | 172 | ||||||

Comments

The lower coil power run may still be isotropic-looking either because of a lack of deposition in the process, or because the bias increases as the coil power is decreased, hence the wafer would have received a more phyisically-aggressive process. Lower temp, lower coil + lower platen may be worth a look.