Specific Process Knowledge/Etch/Etching of Silicon Oxide: Difference between revisions

No edit summary |

|||

| (6 intermediate revisions by 2 users not shown) | |||

| Line 3: | Line 3: | ||

'''All links to Kemibrug (SDS) and Labmanager Including APV and QC requires login.''' | '''All links to Kemibrug (SDS) and Labmanager Including APV and QC requires login.''' | ||

'''Feedback to this page''': '''[mailto:labadviser@ | '''Feedback to this page''': '''[mailto:labadviser@nanolab.dtu.dk?Subject=Feed%20back%20from%20page%20http://labadviser.nanolab.dtu.dk/index.php/Specific_Process_Knowledge/Etch/Etching_of_Silicon_Oxide click here]''' | ||

<!-- Replace "http://labadviser.danchip.dtu.dk/..." with the link to the Labadviser page--> | <!-- Replace "http://labadviser.danchip.dtu.dk/..." with the link to the Labadviser page--> | ||

| Line 44: | Line 44: | ||

*Isotropic etch | *Isotropic etch | ||

| | | | ||

*Anisotropic etch: vertical sidewalls | *Anisotropic etch: vertical sidewalls. | ||

*Primarily for samples with small amounts of metals on. | |||

| | | | ||

*Anisotropic etch: vertical sidewalls | *Anisotropic etch: vertical sidewalls | ||

* | *Primarily for III-V samples | ||

| | | | ||

*Anisotropic etch: vertical sidewalls | *Anisotropic etch: vertical sidewalls | ||

| Line 54: | Line 55: | ||

| | | | ||

*Anisotropic etch: almost vertical sidewalls | *Anisotropic etch: almost vertical sidewalls | ||

*We prefer that SiO2 etch | *We prefer that SiO2 etch takes place in the AOE or Pegasus 4. | ||

| | | | ||

*Primarily for pure physical etch by sputtering with Ar-ions | *Primarily for pure physical etch by sputtering with Ar-ions | ||

*Also for slanted gratings | |||

| | | | ||

*Gas phase HF etching with ethanol as carrier | *Gas phase HF etching with ethanol as carrier | ||

| Line 107: | Line 109: | ||

*Aluminium | *Aluminium | ||

*Chromium | *Chromium | ||

| | | | ||

*Any material that is accepted in the machine | *Any material that is accepted in the machine | ||

| Line 123: | Line 124: | ||

*~80 nm/min (Thermal oxide) in BOE 7:1 Etchant VLSI with Surfactant | *~80 nm/min (Thermal oxide) in BOE 7:1 Etchant VLSI with Surfactant | ||

*~25 nm/min (Thermal oxide) in 5%HF | *~25 nm/min (Thermal oxide) in 5%HF | ||

*~6 nm/min (Thermal oxide) in 1%HF | |||

*~3-4µm/min in 40%HF | *~3-4µm/min in 40%HF | ||

| | | | ||

| Line 277: | Line 279: | ||

<br clear="all" /> | <br clear="all" /> | ||

==Dry etch with Hard mask== | ==Dry etch with Hard mask== | ||

| Line 288: | Line 287: | ||

The recipe ICP is on ICP metal call: A SiO2 etch with C4F8 with resist mask<br> | The recipe ICP is on ICP metal call: A SiO2 etch with C4F8 with resist mask<br> | ||

I had problems with this recipe - it gave polymer on the surface, therefor I do not have more info on that.<br> | I had problems with this recipe - it gave polymer on the surface, therefor I do not have more info on that.<br> | ||

Latest revision as of 14:45, 28 March 2025

Unless anything else is stated, everything on this page, text and pictures are made by DTU Nanolab.

All links to Kemibrug (SDS) and Labmanager Including APV and QC requires login.

Feedback to this page: click here

Comparing silicon oxide etch methods at DTU Nanolab

There are a broad varity of silicon oxide etch methods at DTU Nanolab. The methodes are compared here to make it easier for you to compare and choose the one that suits your needs.

- SiO2 etch using III-V RIE

- SiO2 etch using AOE

- SiO2 etch with DRIE Pegasus 4

- SiO2 etch using ASE

- SiO2 etch using ICP metal

- IBE/IBSD Ionfab 300

- SiO2 etch using Plasma Asher (isotropic)

Compare the methods for Silicon Oxide etching

| Wet Silicon Oxide etch (BHF/HF) | ASE | III-V RIE | AOE (Advanced Oxide Etch) | DRIE Pegasus 4 | ICP metal | IBE/IBSD Ionfab 300 | HF Vapour Phase Etch | |

|---|---|---|---|---|---|---|---|---|

| Generel description |

|

|

|

|

|

|

|

|

| Possible masking materials |

|

|

|

|

|

|

|

|

| Etch rate range |

|

|

|

|

<500nm/min |

|

|

|

| Substrate size |

|

|

|

|

|

|

|

|

| Allowed materials |

In the dedicated bath:

In a plastic beaker:

|

|

|

|

|

|

|

|

Dry etch with Hard mask

By Martin Lind Ommen - fall 2016

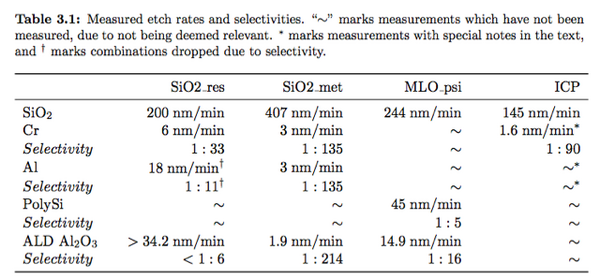

Testing selectivities for SiO2 etching with hard masks on AOE and ICP metal with different recipes.All tests are done with 100% etching load

MLO_psi is the version of SiO2_psi on labadviser that is shown under low line with reduction.

The recipe ICP is on ICP metal call: A SiO2 etch with C4F8 with resist mask

I had problems with this recipe - it gave polymer on the surface, therefor I do not have more info on that.