Specific Process Knowledge/Etch/DRIE-Pegasus: Difference between revisions

| (385 intermediate revisions by 5 users not shown) | |||

| Line 1: | Line 1: | ||

'''Feedback to this page: | |||

[mailto:labadviser@nanolab.dtu.dk?Subject=Feed%20back%20from%20page%20http://labadviser.nanolab.dtu.dk/index.php/Specific_Process_Knowledge/Etch/DRIE-Pegasus click here]''' | |||

[[Category: Equipment |Etch DRIE]] | |||

[[Category: Etch (Dry) Equipment|DRIE]] | |||

The DRIE- | = The DRIE Pegasus tools at DTU Nanolab = | ||

{{Template:Author-jmli1}} | |||

<!--Checked for updates on 2/02-2023 - ok/jmli --> | |||

In 2010 DTU Nanolab acquired DRIE-Pegasus 1 (at the time called Danchip and DRIE-Pegasus, respectively). As a state-of-the-art etch tool with excellent performance and great flexibility, it grew immensely popular and by 2015 it was apparent that we needed yet another tool to cope with the demand. Therefore, in 2016 Pegasus 2 was acquired from a closed-down lab and installed next to Pegasus 1. | |||

Looking to expand our dry etching capabilities in 2017 we got an irresistible offer on a twin Pegasus system with cassette to cassette vacuum robot from a commercial fab. The twin Pegasus system (called Pegasus 3 and 4) is installed at the old cluster 2 location in cleanroom C1 and will run only 6" wafers. Pegasus 3 is the 6" silicon etch work horse and Pegasus 4 is converted (adding extra process gases) into a 6" dielectric etch tool that will supplement/replace the AOE. | |||

[[Specific Process Knowledge/Etch/DRIE-Pegasus/ | This page was originally intended as a regular one-machine page (the Pegasus 1 page). However, as of 2018 with several tools, the page will serve as common page for all of our Pegasi with subpages for each tool. | ||

{| | |||

|width="200"| [[file:DRIE-Pegasus.jpg |200px|frameless]] | |||

| width="400"| [[file:Pegasus 2 operator.jpg |408px|frameless]] | |||

| width="550"|[[file:Peg3and4 front 2.JPG |584px|frameless]] | |||

|- | |||

| align="center" | The DRIE-Pegasus 1 load lock and cassette loader in the DTU Nanolab cleanroom A-1. {{photo1}} | |||

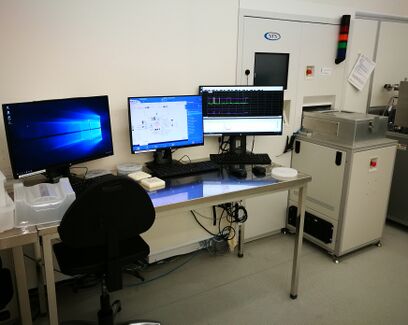

| align="center" | The DRIE-Pegasus 2 operator station and load lock in the DTU Nanolab cleanroom A-1. {{photo1}} | |||

| align="center" | The DRIE-Pegasus3 and DRIE-Pegasus4 operator station and cassette loading stations. {{photo1}} | |||

|- | |||

|} | |||

== The Bosch process == | |||

The DRIE Pegasus tools are state-of-art silicon dry etchers that offer outstanding performance in terms of etch rate, uniformity etc. They use the so-called Bosch process to achieve excellent control of the etched features. Click [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/System-description|'''HERE''']] to access the top of the page. The contents are: | |||

# [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/System-description#Description_of_the_Bosch_process_at_the_DRIE-Pegasus| Description of the Bosch process ]] | |||

# [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/System-description#Processing_options_on_the_Pegasus | Processing options on the Pegasus ]] | |||

# [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/System-description#Modification_of_the_showerhead | Modification of the showerhead ]] | |||

# [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/System-description#RF_Matching | RF matching ]] | |||

## [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/System-description#RF_matching_in_general | RF matching in general ]] | |||

## [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/System-description#Why_RF_matching_is_extremely_important_in_the_Bosch_process | Why RF matching is extremely important in the Bosch process ]] | |||

# [[Specific Process Knowledge/Etch/DRIE-Pegasus/picoscope|Picoscope process monitoring]] | |||

As of 2017, completing the [[LabAdviser/Courses/TPT_Dry_Etch| Dry Etch TPT course]] is mandatory for all new users. On the TPT web page you will find a version of the latest lecture slides - here you will find information as well. | |||

== Links to the individual pages for the Pegasi == | |||

* [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/Pegasus-1|DRIE-Pegasus 1]] | |||

* [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/Pegasus-2|DRIE-Pegasus 2]] | |||

* [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/Pegasus-3|DRIE-Pegasus 3]] | |||

* [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/Pegasus-4|DRIE-Pegasus 4]] | |||

==Equipment performance and process related parameters== | |||

{| border="2" cellspacing="0" cellpadding="1" | |||

!colspan="2" border="none" style="background:silver; color:black;" align="center"|Equipment | |||

|style="background:silver; color:black" width="250" align ="center" |[[Specific Process Knowledge/Etch/DRIE-Pegasus/Pegasus-1| '''DRIE-Pegasus 1''']] | |||

|style="background:silver; color:black" width="250" align ="center" |[[Specific Process Knowledge/Etch/DRIE-Pegasus/Pegasus-2| '''DRIE-Pegasus 2''']] | |||

|style="background:silver; color:black" width="250" align ="center" |[[Specific Process Knowledge/Etch/DRIE-Pegasus/Pegasus-3| '''DRIE-Pegasus 3''']] | |||

|style="background:silver; color:black" width="250" align ="center" |[[Specific Process Knowledge/Etch/DRIE-Pegasus/Pegasus-4| '''DRIE-Pegasus 4''']] | |||

|- | |||

!style="background:silver; color:black;" align="center" valign="center" width="100" rowspan="2"|Purpose | |||

|style="background:Whitesmoke; color:black" width="80" | Primary | |||

|style="background:WhiteSmoke; color:black"| | |||

* Dry etching of 4" silicon | |||

* Dry etching of barc | |||

|style="background:WhiteSmoke; color:black"| | |||

* Research tool | |||

|style="background:WhiteSmoke; color:black"| | |||

* Dry etching of 6" silicon | |||

|style="background:WhiteSmoke; color:black"| | |||

* Dry etching of 6" dielectrics | |||

|- | |||

|style="background:LightGrey; color:black"|Alternative | |||

|style="background:LightGrey; color:black"| | |||

* Black silicon | |||

|style="background:LightGrey; color:black"| | |||

* Backup dry etching of 6" silicon | |||

|style="background:LightGrey; color:black"| | |||

* ? | |||

|style="background:LightGrey; color:black"| | |||

* silicon | |||

|- | |||

!style="background:silver; color:black" align="center" valign="center" rowspan="2"|Performance | |||

|style="background:whitesmoke; color:black"|Etch rates | |||

|style="background:WhiteSmoke; color:black"| | |||

* Standard processes A and B up to 15 µm/min depending on etch load and feature size | |||

* Other processes: Any number from 200 nm/min to 10 µm/min | |||

|style="background:WhiteSmoke; color:black"| | |||

* ? | |||

|style="background:WhiteSmoke; color:black"| | |||

* ? | |||

|style="background:WhiteSmoke; color:black"| | |||

* Depending on the recipe | |||

|- | |||

|style="background:LightGrey; color:black"|Uniformity | |||

|style="background:lightgrey; color:black"| | |||

* For standard processes better than 3 % across a 150 mm wafer. | |||

|style="background:lightgrey; color:black"| | |||

* ? | |||

|style="background:lightgrey; color:black"| | |||

* ? | |||

|style="background:lightgrey; color:black"| | |||

* Depending on the recipe | |||

|- | |||

!style="background:silver; color:black" align="center" valign="center" rowspan="4"|Process parameter range | |||

|style="background:whitesmoke; color:black"|RF powers | |||

|style="background:WhiteSmoke; color:black"| | |||

* Coil Power 5 kW | |||

* Platen power 300/500 W (HF/LF) | |||

|style="background:WhiteSmoke; color:black"| | |||

* Coil Power 5 kW | |||

* Platen power 300/500 W (HF/LF) | |||

|style="background:WhiteSmoke; color:black"| | |||

* Coil Power 5 kW | |||

* Platen power 300/500 W (HF/LF) | |||

|style="background:WhiteSmoke; color:black"| | |||

* Coil Power 5 kW | |||

* Platen power 300/500 W (HF/LF) | |||

|- | |||

|style="background:LightGrey; color:black"|Gas flows | |||

|style="background:lightgrey; color:black"| | |||

* SF<sub>6</sub>: 0 to 1200 sccm | |||

* O<sub>2</sub>: 0 to 200 sccm | |||

* C<sub>4</sub>F<sub>8</sub>: 0 to 400 sccm | |||

* Ar: 0 to 283 sccm | |||

|style="background:lightgrey; color:black"| | |||

* SF<sub>6</sub>-1: 0 to 1200 sccm | |||

* SF<sub>6</sub>-2: 0 to 100 sccm | |||

* O<sub>2</sub>: 0 to 50 sccm | |||

* N<sub>2</sub>: 0 to 500 sccm | |||

* Ar: 0 to 283 sccm | |||

* He: 0 to 11 sccm | |||

|style="background:lightgrey; color:black"| | |||

* SF<sub>6</sub>-1: 0 to 1200 sccm | |||

* SF<sub>6</sub>-2: 0 to 100 sccm | |||

* O<sub>2</sub>: 0 to 200 sccm | |||

* C<sub>4</sub>F<sub>8</sub>: 0 to 400 sccm | |||

* Ar: 0 to 283 sccm | |||

|style="background:lightgrey; color:black"| | |||

{| | |||

*SF<sub>6</sub>: ?(<20) sccm | |||

*O<sub>2</sub>: 200 sccm | |||

*C<sub>4</sub>F<sub>8</sub>: 400 sccm | |||

*Ar: 283 sccm | |||

*He: 500 sccm | |||

*CF<sub>4</sub>: 100 sccm | |||

*H2: 100 sccm | |||

| | |||

| | |||

|} | |||

|- | |||

|style="background:whitesmoke; color:black"|Pressure and temperature | |||

|style="background:WhiteSmoke; color:black"| | |||

* Pressure range 4 to 250 mTorr | |||

* Temperature range -20 to 30 degrees C | |||

|style="background:WhiteSmoke; color:black"| | |||

* Pressure range 4 to 250 mTorr | |||

* Temperature range -20 to 30 degrees C | |||

|style="background:WhiteSmoke; color:black"| | |||

* Pressure range 4 to 250 mTorr | |||

* Temperature range -20 to 30 degrees C | |||

|style="background:WhiteSmoke; color:black"| | |||

* Pressure range 4 to 250 mTorr | |||

* Temperature range -20 to 30 degrees C | |||

|- | |||

|style="background:LightGrey; color:black"|Process options | |||

|style="background:lightgrey; color:black"| | |||

* Bosch processes with etch and dep cycles each split into three | |||

* Parameter ramping during process steps | |||

* SOI option to reduce notching at buried oxide layers | |||

* Picoscope monitoring | |||

* Claritas endpoint detection system | |||

|style="background:lightgrey; color:black"| | |||

* Bosch processes with etch and dep cycles each split into three | |||

* Parameter ramping during process steps | |||

* SOI option to reduce notching at buried oxide layers | |||

* Picoscope monitoring | |||

* Verity OES | |||

|style="background:lightgrey; color:black"| | |||

* Bosch processes with etch and dep cycles each split into three | |||

* Parameter ramping during process steps | |||

* Picoscope monitoring | |||

* SOI option to reduce notching at buried oxide layers | |||

|style="background:lightgrey; color:black"| | |||

* Bosch processes with etch and dep cycles each split into three | |||

* Parameter ramping during process steps | |||

* Verity OES | |||

|- | |||

!style="background:silver; color:black" align="center" valign="center" rowspan="4"|Substrates | |||

|style="background:whitesmoke; color:black"|Sizes | |||

|style="background:WhiteSmoke; color:black"| | |||

* Smaller than 100mm: Bonded to carriers | |||

* 100 mm wafers: Up to 25 wafers in a batch process | |||

|style="background:WhiteSmoke; color:black"| | |||

* Smaller than 150mm: Bonded to carriers | |||

* 150 mm wafers | |||

|style="background:WhiteSmoke; color:black"| | |||

* Smaller than 150mm: Bonded to carriers | |||

* 150 mm wafers | |||

|style="background:WhiteSmoke; color:black"| | |||

* Smaller than 150mm: Bonded to carriers | |||

* 150 mm wafers | |||

|- | |||

| style="background:Lightgrey; color:black"|Loading | |||

|style="background:lightgrey; color:black"| | |||

* Load lock | |||

* MACS (Multiplex Atmospheric Cassette System) | |||

|style="background:lightgrey; color:black"| | |||

* Load lock | |||

|style="background:lightgrey; color:black" colspan="2"| | |||

* Vacuum cassette loader with two cassette stations and shared dealer chamber with Brooks robot | |||

|- | |||

| style="background:Whitesmoke; color:black"|Allowed materials | |||

|style="background:Whitesmoke; color:black"| | |||

* Silicon wafers | |||

* Quartz wafers need a (semi)conducting layer for clamping | |||

|style="background:Whitesmoke; color:black"| | |||

* Silicon wafers | |||

* Quartz wafers need a (semi)conducting layer for clamping | |||

|style="background:Whitesmoke; color:black"| | |||

* Silicon wafers | |||

* Quartz wafers need a (semi)conducting layer for clamping | |||

|style="background:Whitesmoke; color:black"| | |||

* Silicon wafers | |||

* Quartz wafers need a (semi)conducting layer for clamping | |||

|- | |||

| style="background:LightGrey; color:black"|Possible masking materials | |||

|style="background:LightGrey; color:black"| | |||

* AZ photoresist | |||

* zep resist | |||

* DUV stepper resist (barc + krf) | |||

* Oxides and nitrides | |||

* Aluminium (only very gentle processes such as process C and nanoetches) | |||

|style="background:LightGrey; color:black"| | |||

* AZ photoresist | |||

* zep resist | |||

* DUV stepper resist (barc + krf) | |||

* Oxides and nitrides | |||

* Aluminium (only very gentle processes) | |||

|style="background:LightGrey; color:black"| | |||

* AZ and MiR photoresist | |||

* zep resist | |||

* DUV stepper resist (barc + krf) | |||

* Oxides and nitrides | |||

|style="background:LightGrey; color:black"| | |||

* AZ photoresist | |||

* zep resist | |||

* DUV stepper resist (barc + krf) | |||

* Silicon,Oxides and nitrides | |||

* Al, Cr masks | |||

|- | |||

|} | |||

== Process information == | |||

===Process notation=== | |||

Describing a process recipe on the Pegasus may sometimes be difficult because of the great flexibility of the instrument. A compact and precise notation is therefore required for the recipes. Click [[Specific_Process_Knowledge/Etch/DRIE-Pegasus/Notation|'''HERE''']] to find a short description. | |||

===Hardware changes=== | |||

A few hardware modifications have been made on the Pegasus 1 since it was installed in 2010. The changes are listed in the table below under hardware options. | |||

{| border="2" cellspacing="1" cellpadding="1" align="center" | |||

! style="background:silver; color:black" | | |||

! style="background:silver; color:black" | [[Specific Process Knowledge/Etch/DRIE-Pegasus/Pegasus-1| DRIE-Pegasus 1]] | |||

! style="background:silver; color:black" | [[Specific Process Knowledge/Etch/DRIE-Pegasus/Pegasus-2| DRIE-Pegasus 2]] | |||

! style="background:silver; color:black" | [[Specific Process Knowledge/Etch/DRIE-Pegasus/Pegasus-3| DRIE-Pegasus 3]] | |||

! style="background:silver; color:black" | [[Specific Process Knowledge/Etch/DRIE-Pegasus/Pegasus-4| DRIE-Pegasus 4]] | |||

|- valign="top" | |||

! style="background:lightgrey; color:black" | Manufactured | |||

| style="background:lightgrey; color:black" | 2010 | |||

| style="background:lightgrey; color:black" | 2010 | |||

| style="background:lightgrey; color:black" | 2010 | |||

| style="background:lightgrey; color:black" | 2010 | |||

|- valign="top" | |||

! style="background:Whitesmoke; color:black" | Serial | |||

| style="background:WhiteSmoke; color:black" | MP0636 | |||

| style="background:WhiteSmoke; color:black"| MP0641 | |||

| style="background:WhiteSmoke; color:black"| CP0170 | |||

| style="background:WhiteSmoke; color:black"| CP0171 | |||

|- valign="top" | |||

! style="background:lightgrey; color:black" | Electrode size | |||

| style="background:lightgrey; color:black" | 4" | |||

| style="background:lightgrey; color:black" | 6" | |||

| style="background:lightgrey; color:black" | 6" | |||

| style="background:lightgrey; color:black" | 6" | |||

|- valign="top" | |||

! style="background:Whitesmoke; color:black" | Hardware options | |||

| style="background:WhiteSmoke; color:black" | | |||

* [[Specific Process Knowledge/Etch/DRIE-Pegasus/showerheadchange|High flow plenum]] | |||

* [[Specific Process Knowledge/Etch/DRIE-Pegasus/picoscope|Picoscope oscilloscope]] | |||

*[[Specific Process Knowledge/Etch/DRIE-Pegasus/Claritas|Claritas optical endpoint system]] | |||

| style="background:WhiteSmoke; color:black"| | |||

* [[Specific Process Knowledge/Etch/DRIE-Pegasus/showerheadchange|High flow plenum]] | |||

* [[Specific Process Knowledge/Etch/DRIE-Pegasus/picoscope|Picoscope oscilloscope]] | |||

| style="background:WhiteSmoke; color:black"| | |||

* [[Specific Process Knowledge/Etch/DRIE-Pegasus/showerheadchange|High flow plenum]] | |||

* [[Specific Process Knowledge/Etch/DRIE-Pegasus/picoscope|Picoscope oscilloscope]] | |||

| style="background:WhiteSmoke; color:black"| ? | |||

|- | |||

|} | |||

= General Pegasus information = | |||

==Wafer bonding== | |||

To find information on how to bond wafers or chips to a carrier wafer, click [[Specific Process Knowledge/Etch/DryEtchProcessing/Bonding| '''HERE''']]. | |||

==Characterisation of etched trenches== | |||

The trenches in deep silicon trenches can be characterized in many ways. Being able to compare processes requires that a set of common measurements and calculations must be established. Click '''HERE''' to find more information about the parameters used on the DRIE-Pegasus process developme[[Specific Process Knowledge/Etch/DRIE-Pegasus/TrenchCharacterisation|nt]]. | |||

Latest revision as of 14:28, 21 December 2023

Feedback to this page: click here

The DRIE Pegasus tools at DTU Nanolab

Unless otherwise stated, all content on this page was created by Jonas Michael-Lindhard, DTU Nanolab

In 2010 DTU Nanolab acquired DRIE-Pegasus 1 (at the time called Danchip and DRIE-Pegasus, respectively). As a state-of-the-art etch tool with excellent performance and great flexibility, it grew immensely popular and by 2015 it was apparent that we needed yet another tool to cope with the demand. Therefore, in 2016 Pegasus 2 was acquired from a closed-down lab and installed next to Pegasus 1.

Looking to expand our dry etching capabilities in 2017 we got an irresistible offer on a twin Pegasus system with cassette to cassette vacuum robot from a commercial fab. The twin Pegasus system (called Pegasus 3 and 4) is installed at the old cluster 2 location in cleanroom C1 and will run only 6" wafers. Pegasus 3 is the 6" silicon etch work horse and Pegasus 4 is converted (adding extra process gases) into a 6" dielectric etch tool that will supplement/replace the AOE.

This page was originally intended as a regular one-machine page (the Pegasus 1 page). However, as of 2018 with several tools, the page will serve as common page for all of our Pegasi with subpages for each tool.

The Bosch process

The DRIE Pegasus tools are state-of-art silicon dry etchers that offer outstanding performance in terms of etch rate, uniformity etc. They use the so-called Bosch process to achieve excellent control of the etched features. Click HERE to access the top of the page. The contents are:

- Description of the Bosch process

- Processing options on the Pegasus

- Modification of the showerhead

- RF matching

- Picoscope process monitoring

As of 2017, completing the Dry Etch TPT course is mandatory for all new users. On the TPT web page you will find a version of the latest lecture slides - here you will find information as well.

Links to the individual pages for the Pegasi

| Equipment | DRIE-Pegasus 1 | DRIE-Pegasus 2 | DRIE-Pegasus 3 | DRIE-Pegasus 4 | ||

|---|---|---|---|---|---|---|

| Purpose | Primary |

|

|

|

| |

| Alternative |

|

|

|

| ||

| Performance | Etch rates |

|

|

|

| |

| Uniformity |

|

|

|

| ||

| Process parameter range | RF powers |

|

|

|

| |

| Gas flows |

|

|

|

| ||

| Pressure and temperature |

|

|

|

| ||

| Process options |

|

|

|

| ||

| Substrates | Sizes |

|

|

|

| |

| Loading |

|

|

| |||

| Allowed materials |

|

|

|

| ||

| Possible masking materials |

|

|

|

| ||

Process information

Process notation

Describing a process recipe on the Pegasus may sometimes be difficult because of the great flexibility of the instrument. A compact and precise notation is therefore required for the recipes. Click HERE to find a short description.

Hardware changes

A few hardware modifications have been made on the Pegasus 1 since it was installed in 2010. The changes are listed in the table below under hardware options.

| DRIE-Pegasus 1 | DRIE-Pegasus 2 | DRIE-Pegasus 3 | DRIE-Pegasus 4 | |

|---|---|---|---|---|

| Manufactured | 2010 | 2010 | 2010 | 2010 |

| Serial | MP0636 | MP0641 | CP0170 | CP0171 |

| Electrode size | 4" | 6" | 6" | 6" |

| Hardware options | ? |

General Pegasus information

Wafer bonding

To find information on how to bond wafers or chips to a carrier wafer, click HERE.

Characterisation of etched trenches

The trenches in deep silicon trenches can be characterized in many ways. Being able to compare processes requires that a set of common measurements and calculations must be established. Click HERE to find more information about the parameters used on the DRIE-Pegasus process development.