Specific Process Knowledge/Etch/Etching of Silicon Oxide/SiO2 etch using ASE/More test with CF4/H2, CHF3 and C4F8/H2 - SiO2 etch: Difference between revisions

| (3 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

= | =Etch tests of Silicon Oxide= | ||

Tests performed by Maria Farinha @DTU Nanolab | Tests performed by Maria Farinha @DTU Nanolab | ||

| Line 217: | Line 217: | ||

===Recent results - <span style="background:#FFD850">CF<sub>4</sub> / H<sub>2</sub> tests</span> === | ===Recent results - <span style="background:#FFD850">CF<sub>4</sub> / H<sub>2</sub> tests</span> === | ||

The following results were processed on chips bonded to a 100mm wafer. They were patterned with 915 UVN resist (DUV negative) and 65nm of BARC. The SiO2 layer was 2um (deposited on the C1 furnace). | The following results were processed on chips bonded to a 100mm wafer. They were patterned with 915 UVN resist (DUV negative) and 65nm of BARC. The SiO2 layer was 2um (deposited on the C1 furnace). <br> | ||

(25 jan 2024) | |||

| Line 325: | Line 326: | ||

|- | |- | ||

|} | |} | ||

=Etch test of Silicon Nitride= | |||

* The nitride layer deposited was 560nm, on the PECVD4 (recipe: Standard HF SiN with wafer clean, for 1h). <br> | |||

* They were patterned with 750 DUV resist and 65nm of BARC (exposure:355 J/m2, focus:-3.1). <br> | |||

* The following results were processed on chips (2*2cm) bonded to a 100mm dummy wafer. | |||

{| border="1" cellspacing="1" cellpadding="1" | |||

! '''Recipe''' | |||

! '''Time (min)''' | |||

! '''Date''' | |||

! '''SEM picture''' | |||

! '''Redeposition - top view''' | |||

! '''Etch rate SiN (nm/min)''' | |||

! '''Etch rate resist (nm/min)''' | |||

! '''Selectivity <br> (SiN:resist)''' | |||

|- | |||

|- | |||

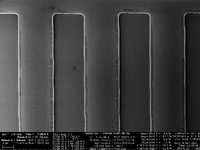

|-style="background:white; color:black" | |||

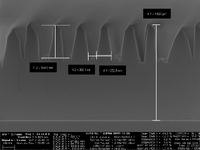

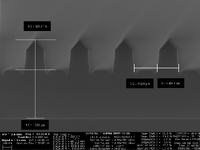

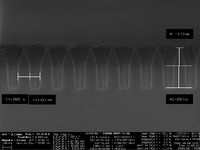

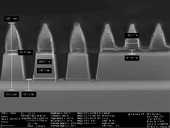

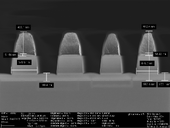

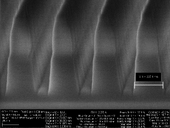

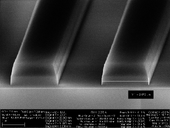

|<!-- '''Recipe name''' --> '''CF4lowCP''' <br> CF<sub>4</sub>= 22.5 sccm <br> H<sub>2</sub>= 22.5 sccm <br> Coil= 150W <br> Platen= '''45W''' <br> Press= 2.5mTorr <br> Temp= 20°C <br> | |||

|<!--'''Process time'''--> 5:00 | |||

|<!--'''Date'''--> 29/02<br>-2024 | |||

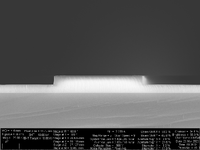

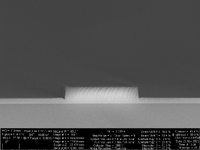

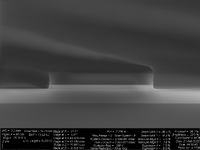

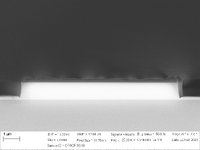

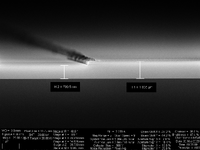

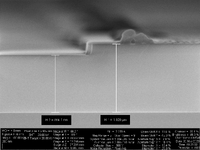

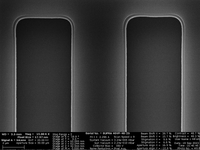

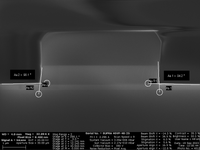

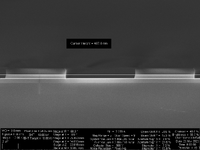

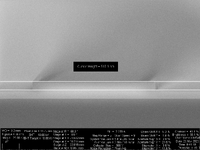

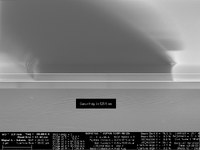

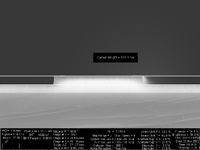

|<!--'''SEM picture'''--> [[File:Si3N4 pat3 cf4lowcp- 250.png|170px]] [[File:Si3N4 pat3 cf4lowcp- 500.png|170px]] [[File:Si3N4 pat3 cf4lowcp- 1000.png|170px]] [[File:Si3N4 pat3 cf4lowcp- 2000.png|170px]] | |||

|<!--'''Redeposition - top view'''--> [[File:SiN cf4lowcp sidewalls 01.png|170px]] [[File:SiN cf4lowcp sidewalls 02.png|170px]] | |||

|<!--'''Etch rate in SiO2'''-->250nm- 76,50 <br> <br>500nm- 73,92 <br> <br>1000nm- 73,94 <br> <br>2000nm- 76,50 | |||

|<!--'''Etch rate in resist'''-->250nm- 44,98 <br> <br>500nm- 33,52 <br> <br>1000nm- 31,16 <br> <br>2000nm- 25,66 | |||

|<!--'''Selectivity (SiO2:resist)'''-->250nm- 1,70 <br> <br>500nm- 2,21 <br> <br>1000nm- 2,37 <br> <br>2000nm- 2,98 | |||

|- | |||

|- | |||

|} | |||

<br clear="all" /> | |||

Latest revision as of 11:54, 29 April 2024

Etch tests of Silicon Oxide

Tests performed by Maria Farinha @DTU Nanolab

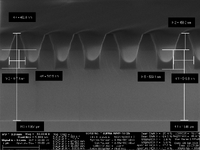

The gas flows were combined and the following results were achieved. It´s visible that with higher CF4 the selectivity is not good, so by adding H2, until 1:1, the selectivity improves. Additionally, the uniformity gets slightly worse while going for 1:1 of gas chemistry.

The recipe CF4lowCP 22.5/22.5 seems to be the only one good enough to use. It is a slow etch recipe, with good selectivity with AZ5214E resist.

| CF4ICP | SiO2 ER (nm/min) | Uniformity (SiO2 etch) | Selectivity (SiO2:resist) | Si3N4 ER (nm/min) | SixN ER (nm/min) |

|---|---|---|---|---|---|

| 45 CF4 + 0 H2 | |||||

| 35 CF4 + 10 H2 | |||||

| 22.5 CF4 + 22.5 H2 |

- The uniformity considers a 100mm wafer, calculated with 5 points.

| CF4lowCP | SiO2 ER (nm/min) | Uniformity (SiO2 etch) | Selectivity (SiO2:resist) | Si3N4 ER (nm/min) | SixN ER (nm/min) |

|---|---|---|---|---|---|

| 45 CF4 + 0 H2 | |||||

| 35 CF4 + 10 H2 | |||||

| 22.5 CF4 + 22.5 H2 |

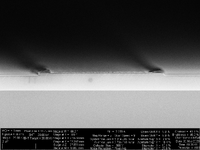

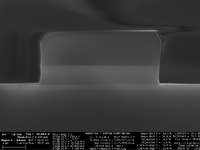

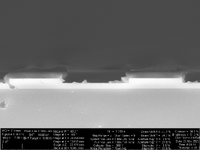

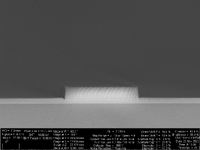

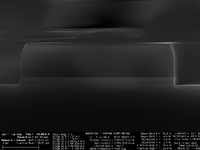

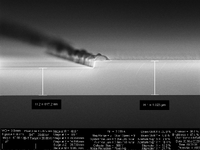

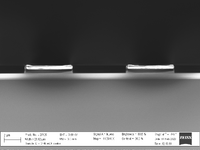

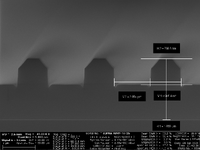

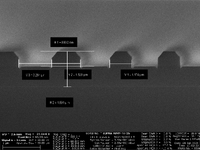

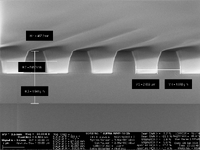

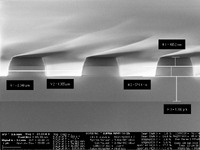

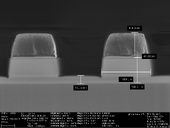

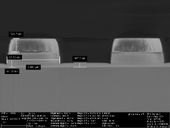

Profile pictures of some tests - April 2023

Even in the cases with the resist strip (plasma asher 2 processing for 10/15min), there are some traces of resist left on the edges of the features.

Also, it´s noticeable that the feature profile is trenching, being more evident with faster etch rates.

Recipes and results - CF4 / H2 tests

Recent results - CF4 / H2 tests

The following results were processed on chips bonded to a 100mm wafer. They were patterned with 915 UVN resist (DUV negative) and 65nm of BARC. The SiO2 layer was 2um (deposited on the C1 furnace).

(25 jan 2024)

Etch test of Silicon Nitride

- The nitride layer deposited was 560nm, on the PECVD4 (recipe: Standard HF SiN with wafer clean, for 1h).

- They were patterned with 750 DUV resist and 65nm of BARC (exposure:355 J/m2, focus:-3.1).

- The following results were processed on chips (2*2cm) bonded to a 100mm dummy wafer.