LabAdviser/Technology Research/Fabrication of Hyperbolic Metamaterials using Atomic Layer Deposition/AZO gratings

Procces flow description

Si template fabrication

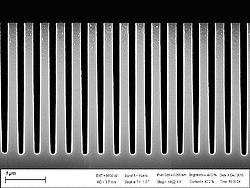

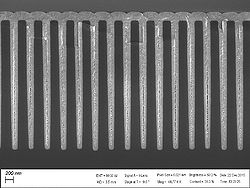

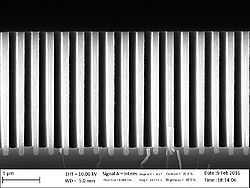

The whole fabrication work took place in a class 100 cleanroom. First, standard double side polished Si (100) wafers were selected and RCA cleaned. Conventional deep-UV lithography (DUV stepper: Canon FPA-3000 EX4) was implemented for defining the grating patterns (lines 200 nm wide and 400 nm pitch) on 22 cm2 scale chips. The normal procedure includes bottom antireflective coating (BARC) and photoresist spinning, followed by spray developing. To promote adhesion and to minimize interference effects, the substrate surface was coated with a 65 nm thick BARC coating (DUV42S-6, Brewer Science, USA) followed by a bake-out at 175°C for 60 s. The positive photoresist (KRF M230Y, JSR Micro, NV) was spin-coated to a thickness of 360 nm and baked at 130°C for 90 s. Thereafter, deep reactive ion etching (DRIE) was used to fabricate trenches in the silicon substrate with a depth of 3 μm.

Process flow

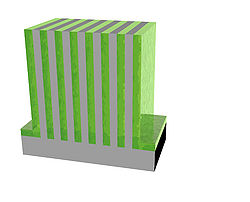

Description of steps for fabrication of AZO nanogratings.

| Step | Description | LabAdviser link | Image showing the step | |

|---|---|---|---|---|

| 1.1 | Plasma surface treatment | To ensure clean surface, the 100 mm Si wafer is treated by O2/N2 plasma. (Optional step) | Plasma Asher 2 | |

| 1.2 | DUV Resist patterning | DUV | DUV Stepper Lithography. | |

| 1.3 | Deep reactive ion etching (DRIE) | DRIE; Recipe: PolySOI10 Recipe needs to be tuned. Adjusted parameters: temperature, etching and passivation times. | DRIE Pegasus. | |

| 1.4 | Plasma surface treatment | To ensure that remainings of DUV resist are gone, samples are treated by O2/N2 plasma. (Optional step) | ||

| 1.5 | Scanning Electron Microscopy inspection | By cleaving the sample it is possible to inspect DRIE etched Si trenches in cross-sectional mode | ||

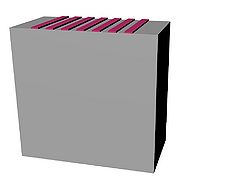

| 1.6 | Atomic Layer Deposition of Al-doped ZnO (AZO) | Deposition carried at 200oC. Thickness is above 100 nm. | Equipment used: ALD Picosun R200. Standard recipe used: AZO 20T. | |

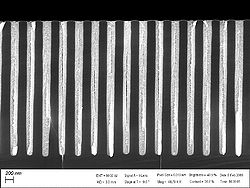

| 1.7 | Scanning Electron Microscopy inspection | By cleaving the sample it is possible to inspect ALD coatings deposited on Si trenches in cross-sectional mode | ||

| 1.8 | Ion Beam Etching (IBE). | Opening of deposited AZO top layer using recipe "Ti acceptance" there the stage was placed to 0o degree. The back side of the wafer also needs to be exposed to etching. | IBE/IBSD Ionfab 300 | |

| 1.9 | Scanning Electron Microscopy inspection | By cleaving the sample it is possible to inspect IBE etching results in cross-sectional mode | ||

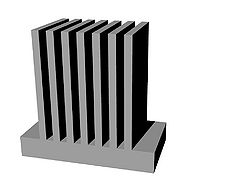

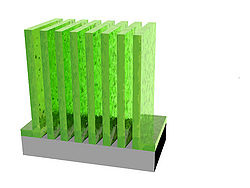

| 1.10 | Selective etch of Si between ALD AZO coatings. | Si etching proceeds using reactive ion etching with isotropic process based on SF6 process gas. | Equipment used: RIE2. | |

| 1.11 | Scanning Electron Microscopy inspection of fabricated structure. | Proof of final result. | ||