Specific Process Knowledge/Lithography/EBeamLithography/JEOLAlignment: Difference between revisions

| Line 5: | Line 5: | ||

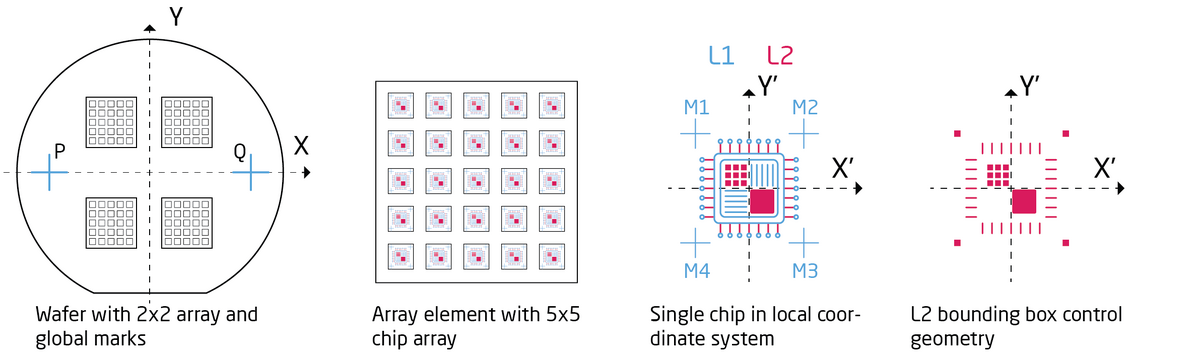

The job illustrated below writes a chip layout in a 5 x 5 matrix into a 2 x 2 matrix as illustrated in the figure. The first layer, L1, has defined global marks at P = (-30000,0) and Q = (30000,0). The local chip marks are placed at M1 = (-450,450), M2 = (450,450), M3 = (450,-450) and M4=(-450,-450). First a global alignment is called via the '''GLMDET''' command and subsequently chip alignment is called using the '''CHIPAL''' command. The mark positions are stated in the JDF file using the '''GLMPOS''' command for PQ marks and the '''M1''' to '''M4''' commands for chip marks. Remember that a V30 file is placed relative to its bounding box center coordinate and hence it might be necessary to control the bounding box extents by adding control geometry (corner marks) if the design is not symmetric around (0,0) in the chip design coordinate system. | The job illustrated below writes a chip layout in a 5 x 5 matrix into a 2 x 2 matrix as illustrated in the figure. The first layer, L1, has defined global marks at P = (-30000,0) and Q = (30000,0). The local chip marks are placed at M1 = (-450,450), M2 = (450,450), M3 = (450,-450) and M4=(-450,-450). First a global alignment is called via the '''GLMDET''' command and subsequently chip alignment is called using the '''CHIPAL''' command. The mark positions are stated in the JDF file using the '''GLMPOS''' command for PQ marks and the '''M1''' to '''M4''' commands for chip marks. Remember that a V30 file is placed relative to its bounding box center coordinate and hence it might be necessary to control the bounding box extents by adding control geometry (corner marks) if the design is not symmetric around (0,0) in the chip design coordinate system. | ||

{| style="border: none; border-spacing: 0; margin: 1em auto; text-align: | {| style="border: none; border-spacing: 0; margin: 1em auto; text-align: left;" | ||

|- | |- | ||

| [[image:EBLChipAlignExample.png|1200px]] | | [[image:EBLChipAlignExample.png|1200px]] | ||

Revision as of 23:10, 5 May 2023

Aligned exposure on JEOL 9500

There is quite a few things to remember in order to align an exposure to an existing pattern. The example below is a step by step guide illustrating global substrate alignment as well as chip alignment. If your job only requires global alignment simply skip the chip alignment part. In the example we assume a layer, L1, is already defined on the substrate and the goal is to align the next layer, L2, to it.

Job preparation

The job illustrated below writes a chip layout in a 5 x 5 matrix into a 2 x 2 matrix as illustrated in the figure. The first layer, L1, has defined global marks at P = (-30000,0) and Q = (30000,0). The local chip marks are placed at M1 = (-450,450), M2 = (450,450), M3 = (450,-450) and M4=(-450,-450). First a global alignment is called via the GLMDET command and subsequently chip alignment is called using the CHIPAL command. The mark positions are stated in the JDF file using the GLMPOS command for PQ marks and the M1 to M4 commands for chip marks. Remember that a V30 file is placed relative to its bounding box center coordinate and hence it might be necessary to control the bounding box extents by adding control geometry (corner marks) if the design is not symmetric around (0,0) in the chip design coordinate system.

The following SDF and JDF files will be used for the example.

;SDF MAGAZIN 'THOPE' #8 %4C JDF 'thope230126',1 ACC 100 CALPRM '6na_ap5' DEFMODE 2 GLMDET A CHIPAL 1 HSWITCH OFF,ON RESIST 250 SHOT A,6 OFFSET(-44,-139) END 8 |

;JDF

JOB/W 'THOPE',4 ; 4inch wafer

GLMPOS P=(-30000,0),Q=(30000,0)

PATH FT01

ARRAY (-15000,2,30000)/(10000,2,20000)

ASSIGN A(1) -> ((1,1))

1: ARRAY (-4000,5,2000)/(4000,5,2000)

CHMPOS M1=(-450,450),M2=(450,450),M3=(450,-450),M4=(-450,-450)

ASSIGN P(1) -> (*,*)

AEND

PEND

LAYER 1

P(1) 'thope230126.v30'

SPPRM 4.0,,,,1.0,1

STDCUR 6

END

| |

;SDF MAGAZIN 'THOPE' #8 %4C JDF 'thope230126',1 ACC 100 CALPRM '6na_ap5' DEFMODE 2 GLMDET A CHIPAL 1 HSWITCH OFF,ON RESIST 250 SHOT A,6 OFFSET(-44,-139) END 8

;JDF

JOB/W 'THOPE',4 ; 4inch wafer

GLMPOS P=(-30000,0),Q=(30000,0)

PATH FT01

ARRAY (-15000,2,30000)/(10000,2,20000)

ASSIGN A(1) -> ((1,1))

1: ARRAY (-4000,5,2000)/(4000,5,2000)

CHMPOS M1=(-450,450),M2=(450,450),M3=(450,-450),M4=(-450,-450)

ASSIGN P(1) -> (*,*)

AEND

PEND

LAYER 1

P(1) 'thope230126.v30'

SPPRM 4.0,,,,1.0,1

STDCUR 6

END

CHMPOS [M1=(x1,y1){,M2=(x2,y2),M3=(x3,y3),M4=(x4,y4)}]

CHMPOS defines the chip alignment marks in the local chip coordinate system, unit is µm. M1 is mandatory while M2-M4 are optional in one mark mode. In four mark mode all marks must be defined. The order of the marks is important, M1 must be top left with M2-M4 placed clockwise around the center. In the given example the four marks are placed symmetrically at ±450 µm in x and ±450 µm in y.

It V1 mode it is customary to set M1 = (0,0) such that substrate height is detected at the center of the chip. In this way V1 mode can be used to exactly read out substrate height where the chip pattern will be written.