Specific Process Knowledge/Etch/Etching of Silicon Oxide/SiO2 etch using ASE: Difference between revisions

| Line 8: | Line 8: | ||

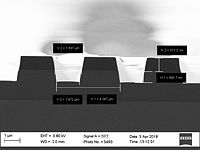

Our old RIE systems have to the end of their lives been used a lot for etching samples that could not be clamped/cooled in the ICP systems. The higher plasma density in the ICP's make their processes more tough on resist masks, probably because of too much heating. Therefor the ICP's are using cooled bottom electrodes with He back side cooling to keep the temperature low for the resist mask to survive. When decommissioning the RIE's (RIE1 and RIE2) a need came for developing recipes on the ICP's that could etch Si, SiO2 and SiN without clamping/cooling the substrates. This part consideres eting in SIO2. First an attempt to run the ASE in RIE mode using only the platen generator was made. This resulted in not so nice sidewalls due to redeposition and low etches, see below. After that the development focused on running with both low coil power and low platen power. | Our old RIE systems have to the end of their lives been used a lot for etching samples that could not be clamped/cooled in the ICP systems. The higher plasma density in the ICP's make their processes more tough on resist masks, probably because of too much heating. Therefor the ICP's are using cooled bottom electrodes with He back side cooling to keep the temperature low for the resist mask to survive. When decommissioning the RIE's (RIE1 and RIE2) a need came for developing recipes on the ICP's that could etch Si, SiO2 and SiN without clamping/cooling the substrates. This part consideres eting in SIO2. First an attempt to run the ASE in RIE mode using only the platen generator was made. This resulted in not so nice sidewalls due to redeposition and low etches, see below. After that the development focused on running with both low coil power and low platen power. | ||

==SiO2 etch with resist mask, sample on carrier (Si carrier) in the RIE mode using CF4/CFH3/H2 chemistry== | |||

''By Berit Herstrøm @danchip, January-Marts 2018'' | |||

==SiO2 etch with resist mask, sample on carrier (Si carrier) in the ICP mode using C4F8/H2 chemistry== | ==SiO2 etch with resist mask, sample on carrier (Si carrier) in the ICP mode using C4F8/H2 chemistry== | ||

Revision as of 15:46, 6 April 2018

Feedback to this page: click here

THIS PAGE IS UNDER CONSTRUCTION

Development work: SiO2 etch with resist mask, sample on carrier (Si carrier)

Our old RIE systems have to the end of their lives been used a lot for etching samples that could not be clamped/cooled in the ICP systems. The higher plasma density in the ICP's make their processes more tough on resist masks, probably because of too much heating. Therefor the ICP's are using cooled bottom electrodes with He back side cooling to keep the temperature low for the resist mask to survive. When decommissioning the RIE's (RIE1 and RIE2) a need came for developing recipes on the ICP's that could etch Si, SiO2 and SiN without clamping/cooling the substrates. This part consideres eting in SIO2. First an attempt to run the ASE in RIE mode using only the platen generator was made. This resulted in not so nice sidewalls due to redeposition and low etches, see below. After that the development focused on running with both low coil power and low platen power.

SiO2 etch with resist mask, sample on carrier (Si carrier) in the RIE mode using CF4/CFH3/H2 chemistry

By Berit Herstrøm @danchip, January-Marts 2018

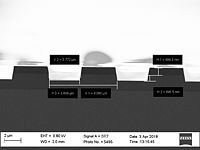

SiO2 etch with resist mask, sample on carrier (Si carrier) in the ICP mode using C4F8/H2 chemistry

By Berit Herstrøm @danchip, January-Marts 2018

The challenge was to develop a SiO2 etching recipe that can be used for samples on a carrier. Samples that cannot be clamped and cooled. The goal was to keep a good selectivity to the resist mask and get a vertical sidewall, without getting a lot of redeposition on the sidewalls. The testing regime was using both the coil power and the platen power with C4F8/H2 chemistry.

Take a look at development flow and the results here: Media:ASE SiO2 etch on carrier ICP C4F8 H2 no He rev02.pdf . Zoom in to read and see the images: (Ctrl + "+")

Take a look at development flow and the results here: Media:ASE SiO2 etch on carrier ICP C4F8 H2 no He rev02.pdf . Zoom in to read and see the images: (Ctrl + "+")

The recommended recipe for SiO2 etch using a carrier is this

| Parameter | Recipe name: 1SiO2_02 |

|---|---|

| Coil Power [W] | 150 |

| Platen Power [W] | 25 |

| Platen temperature [oC] | 20 |

| C4F8 flow [sccm] | 36 |

| H2 flow [sccm] | 13 |

| Pressure [mTorr] | 2.5 |

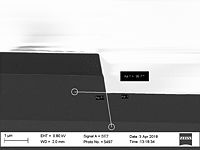

Results for 1SiO2_02 on a piece of wafer on a Si carrier

| Material to be etched | Etch rate using SiO2_res |

|---|---|

| Etch rate in SiO2 | 22.1 nm/min |

| Etch rate in resist (MIR) | 12.5 nm/min |

| Selectivity (SiO2:resist) | 1.8 |

| Profile Images |

|