Specific Process Knowledge/Etch/Etching of Silicon Oxide/SiO2 etch using ASE: Difference between revisions

Jump to navigation

Jump to search

THIS PAGE IS UNDER CONSTRUCTION

| Line 39: | Line 39: | ||

|} | |} | ||

===Results for 1SiO2_02 on a piece of wafer on a Si carrier === | ====Results for 1SiO2_02 on a piece of wafer on a Si carrier ==== | ||

{| border="2" cellspacing="2" cellpadding="3" | {| border="2" cellspacing="2" cellpadding="3" | ||

Revision as of 13:44, 5 April 2018

Feedback to this page: click here

THIS PAGE IS UNDER CONSTRUCTION

Development work: SiO2 etch with resist mask, sample on carrier (Si carrier)

By Berit Herstrøm @danchip, January-Marts 2018

The challenge was to develop a SiO2 etching recipe that can be used for samples on a carrier. Samples that cannot be clamped and cooled. The goal was to keep a good selectivity to the resist mask and get a vertical sidewall, without getting a lot of redeposition on the sidewalls. The testing regime was using both the coil power and the platen power with C4F8/H2 chemistry.

Take a look at development flow and the results here: Media:ASE SiO2 etch on carrier ICP C4F8 H2 no He rev02.pdf . Zoom in to read and see the images: (Ctrl + "+")

Take a look at development flow and the results here: Media:ASE SiO2 etch on carrier ICP C4F8 H2 no He rev02.pdf . Zoom in to read and see the images: (Ctrl + "+")

The recommended recipe for SiO2 etch using a carrier is this

| Parameter | Recipe name: 1SiO2_02 |

|---|---|

| Coil Power [W] | 150 |

| Platen Power [W] | 25 |

| Platen temperature [oC] | 20 |

| C4F8 flow [sccm] | 36 |

| H2 flow [sccm] | 13 |

| Pressure [mTorr] | 2.5 |

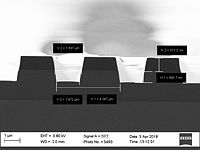

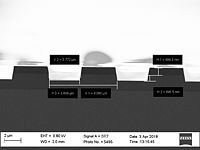

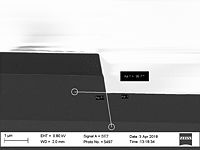

Results for 1SiO2_02 on a piece of wafer on a Si carrier

| Material to be etched | Etch rate using SiO2_res |

|---|---|

| Etch rate in SiO2 | 22.1 nm/min |

| Etch rate in resist (MIR) | 12.5 nm/min |

| Selectivity (SiO2:resist) | 1.8 |

| Profile Images |

|