Specific Process Knowledge/Thin Film deposition/ALD/TiO2 deposition using ALD: Difference between revisions

| Line 8: | Line 8: | ||

A low temperatures between 120 <sup>o</sup>C and 150 <sup>o</sup>C an amorphous TiO<sub>2</sub> layer is grown in the ALD, and at higher temperatures between 300 <sup>o</sup>C and 350 <sup>o</sup>C an anatase TiO<sub>2</sub> layer is grown. At temperatures between 150 <sup>o</sup>C and 300 <sup>o</sup>C the TiO<sub>2</sub> layer will be a mixture of both amorphous and anatase TiO<sub>2</sub>. | A low temperatures between 120 <sup>o</sup>C and 150 <sup>o</sup>C an amorphous TiO<sub>2</sub> layer is grown in the ALD, and at higher temperatures between 300 <sup>o</sup>C and 350 <sup>o</sup>C an anatase TiO<sub>2</sub> layer is grown. At temperatures between 150 <sup>o</sup>C and 300 <sup>o</sup>C the TiO<sub>2</sub> layer will be a mixture of both amorphous and anatase TiO<sub>2</sub>. | ||

For Si wafers, | For Si wafers, amorphous TiO<sub>2</sub> is best grown on wafers with native oxide, and anatase TiO<sub>2</sub> is best grown on wafers without native oxide (removed using HF). | ||

===TiO<sub>2</sub> standard recipe=== | ===TiO<sub>2</sub> standard recipe=== | ||

| Line 35: | Line 35: | ||

|- | |- | ||

|} | |} | ||

===TiO<sub>2</sub> deposition rates=== | ===TiO<sub>2</sub> deposition rates=== | ||

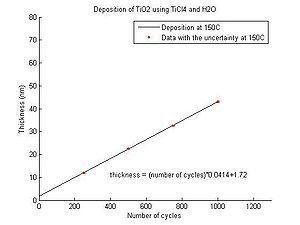

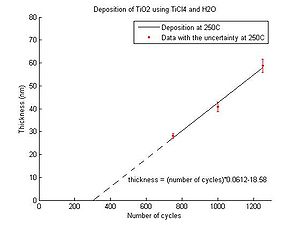

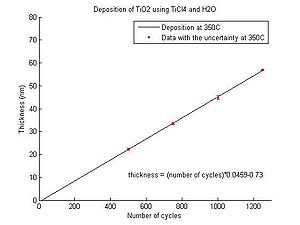

In the graphs below the TiO<sub>2</sub> thickness as function of the number of cycles for deposition temperatures between 150 <sup>o</sup>C and 350 <sup>o</sup>C can be seen. From the equations the number of cycles required for a certain thickess can be calculated. All | In the graphs below the TiO<sub>2</sub> thickness as function of the number of cycles for deposition temperatures between 150 <sup>o</sup>C and 350 <sup>o</sup>C can be seen. From the equations the number of cycles required for a certain thickess to be deposited can be calculated. All results have been obtained for Si wafers with native oxide. | ||

<gallery caption="Titanium dioxide thickness as function of number of cycles" widths="300px" heights="300px" perrow="3"> | <gallery caption="Titanium dioxide thickness as function of number of cycles" widths="300px" heights="300px" perrow="3"> | ||

| Line 48: | Line 49: | ||

===TiO<sub>2</sub> results=== | ===TiO<sub>2</sub> results=== | ||

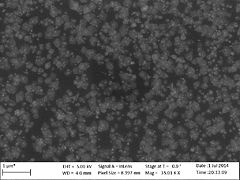

Some some SEM images of TiO<sub>2</sub> deposited on a Si surface at different temperatures between 150 <sup>o</sup>C and 350 <sup>o</sup>C are shown below. Some of samples have been treated with HF (hydrofluoric acid) to remove the native oxide layer | Some some SEM images of TiO<sub>2</sub> deposited on a Si surface at different temperatures between 150 <sup>o</sup>C and 350 <sup>o</sup>C are shown below. Some of samples have been treated with HF (hydrofluoric acid) to remove the native oxide layer just before the ALD deposition. | ||

<gallery caption="Titanium dioxide deposited at different temperatures on a Si surface" widths="250px" heights=" | <gallery caption="Titanium dioxide deposited at different temperatures on a Si surface" widths="250px" heights="180px" perrow="3"> | ||

image:TiO2 150C 1200 cycles Si_HF_treated.jpg| Temperature 150 <sup>o</sup>C, 1200 cycles, HF treated. | image:TiO2 150C 1200 cycles Si_HF_treated.jpg| Temperature 150 <sup>o</sup>C, 1200 cycles, HF treated. | ||

image:TiO2 150C 1200 cycles Si_untreated.jpg| Temperature 150 <sup>o</sup>C, 1200 cycles. | image:TiO2 150C 1200 cycles Si_untreated.jpg| Temperature 150 <sup>o</sup>C, 1200 cycles. | ||

image:TiO2 250C 750cycles_Si_untreated.jpg| Temperature 250 <sup>o</sup>C, 750 cycles. | image:TiO2 250C 750cycles_Si_untreated.jpg| Temperature 250 <sup>o</sup>C, 750 cycles. | ||

</gallery> | </gallery> | ||

<gallery caption="" widths="250px" heights=" | <gallery caption="" widths="250px" heights="180px" perrow="5"> | ||

image:TiO2 1000 cycles 300C Si_HF.jpg| Temperature 300 <sup>o</sup>C, 1000 cycles, HF treated. | image:TiO2 1000 cycles 300C Si_HF.jpg| Temperature 300 <sup>o</sup>C, 1000 cycles, HF treated. | ||

image:TiO2 1000 cycles 300C Si_un.jpg| Temperature 300 <sup>o</sup>C, 1000 cycles. | image:TiO2 1000 cycles 300C Si_un.jpg| Temperature 300 <sup>o</sup>C, 1000 cycles. | ||

| Line 61: | Line 62: | ||

</gallery> | </gallery> | ||

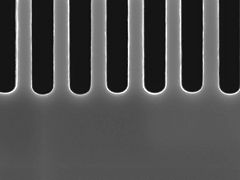

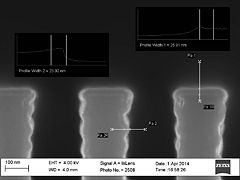

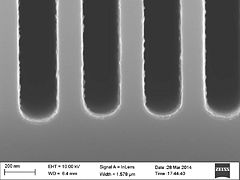

Below some SEM images of | Below some SEM images of amorphous TiO<sub>2</sub> deposited at 120 <sup>o</sup>C on Si trenches are shown. The width of the trenches is 200 nm, and the depth is 4 µm, i.e. the aspect ratio is 1:20. The number of cycles is 500, and this results in a TiO<sub>2</sub> layer of about 25 nm. From the SEM images it is seen that the TiO<sub>2</sub> layer covers the trenches very well. | ||

<gallery caption=" | <gallery caption="Amorphous titanium dioxide deposited on Si trenches" widths="250px" heights="180px" perrow="3"> | ||

image:SEM-TiO2-120C-1.jpg| | image:SEM-TiO2-120C-1.jpg| | ||

image:SEM-TiO2-120C-2.jpg| | image:SEM-TiO2-120C-2.jpg| | ||

| Line 69: | Line 70: | ||

</gallery> | </gallery> | ||

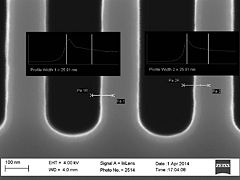

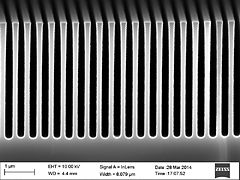

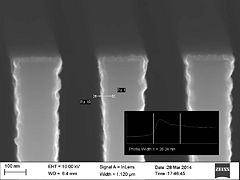

Below some SEM images of | Below some SEM images of anatase TiO<sub>2</sub> deposited at 300 <sup>o</sup>C on Si trenches are shown. The width of the trenches is 200 nm, and the depth is 4 µm, i.e. the aspect ratio is 1:20. The number of cycles is 500, and this results in a TiO<sub>2</sub> layer of about 26 nm. From the SEM images it is seen that the TiO<sub>2</sub> layer covers the trenches very well. | ||

<gallery caption=" | <gallery caption="Anastase titanium dioxide deposited on Si trenches" widths="250px" heights="180px" perrow="3"> | ||

image:TiO2 trenches-300C-1.jpg| | image:TiO2 trenches-300C-1.jpg| | ||

image:TiO2 trenches-300C-2.jpg| | image:TiO2 trenches-300C-2.jpg| | ||

| Line 79: | Line 80: | ||

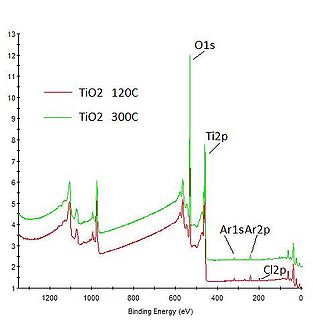

XPS measurements of TiO<sub>2</sub> deposited at 120 <sup>o</sup>C and 300 <sup>o</sup>C are shown below. From the XPS measurements it can be calculated that at temperaturs below 120 <sup>o</sup>C the TiO<sub>2</sub> layer will be contaminated with about 1-3 % chlorine molecules from the TiCl<sub>4</sub> precursor. This can be also seen as small white dots in SEM images of the anatase TiO<sub>2</sub> layers above. | XPS measurements of TiO<sub>2</sub> deposited at 120 <sup>o</sup>C and 300 <sup>o</sup>C are shown below. From the XPS measurements it can be calculated that at temperaturs below 120 <sup>o</sup>C the TiO<sub>2</sub> layer will be contaminated with about 1-3 % chlorine molecules from the TiCl<sub>4</sub> precursor. This can be also seen as small white dots in SEM images of the anatase TiO<sub>2</sub> layers above. | ||

[[image:XPS_TiO2.jpg|320x320px|left|thumb|XPS measurements of titanium dioxide]] | [[image:XPS_TiO2.jpg|320x320px|left|thumb|XPS measurements of titanium dioxide.]] | ||

Revision as of 11:41, 3 July 2015

THIS PAGE IS UNDER CONSTRUCTION

Feedback to this page: click here

The ALD window for titanium dioxide (TiO2) ranges from 120 oC to 350 oC.

A low temperatures between 120 oC and 150 oC an amorphous TiO2 layer is grown in the ALD, and at higher temperatures between 300 oC and 350 oC an anatase TiO2 layer is grown. At temperatures between 150 oC and 300 oC the TiO2 layer will be a mixture of both amorphous and anatase TiO2.

For Si wafers, amorphous TiO2 is best grown on wafers with native oxide, and anatase TiO2 is best grown on wafers without native oxide (removed using HF).

TiO2 standard recipe

Recipe: TiO2

Temperature: 120 oC - 350 oC

| TiCl4 | H2O | |

|---|---|---|

| Nitrogen flow | 150 sccm | 200 sccm |

| Pulse time | 0.1 s | 0.1 s |

| Purge time | 3.0 s | 4.0 s |

TiO2 deposition rates

In the graphs below the TiO2 thickness as function of the number of cycles for deposition temperatures between 150 oC and 350 oC can be seen. From the equations the number of cycles required for a certain thickess to be deposited can be calculated. All results have been obtained for Si wafers with native oxide.

- Titanium dioxide thickness as function of number of cycles

-

Temperature 150 oC.

-

Temperature 250 oC.

-

Temperature 350 oC.

TiO2 results

Some some SEM images of TiO2 deposited on a Si surface at different temperatures between 150 oC and 350 oC are shown below. Some of samples have been treated with HF (hydrofluoric acid) to remove the native oxide layer just before the ALD deposition.

- Titanium dioxide deposited at different temperatures on a Si surface

-

Temperature 150 oC, 1200 cycles, HF treated.

-

Temperature 150 oC, 1200 cycles.

-

Temperature 250 oC, 750 cycles.

-

Temperature 300 oC, 1000 cycles, HF treated.

-

Temperature 300 oC, 1000 cycles.

-

Temperature 350 oC, 1250 cycles, HF treated.

Below some SEM images of amorphous TiO2 deposited at 120 oC on Si trenches are shown. The width of the trenches is 200 nm, and the depth is 4 µm, i.e. the aspect ratio is 1:20. The number of cycles is 500, and this results in a TiO2 layer of about 25 nm. From the SEM images it is seen that the TiO2 layer covers the trenches very well.

- Amorphous titanium dioxide deposited on Si trenches

Below some SEM images of anatase TiO2 deposited at 300 oC on Si trenches are shown. The width of the trenches is 200 nm, and the depth is 4 µm, i.e. the aspect ratio is 1:20. The number of cycles is 500, and this results in a TiO2 layer of about 26 nm. From the SEM images it is seen that the TiO2 layer covers the trenches very well.

- Anastase titanium dioxide deposited on Si trenches

XPS measurements of TiO2 deposited at 120 oC and 300 oC are shown below. From the XPS measurements it can be calculated that at temperaturs below 120 oC the TiO2 layer will be contaminated with about 1-3 % chlorine molecules from the TiCl4 precursor. This can be also seen as small white dots in SEM images of the anatase TiO2 layers above.

Evgeniy Shkondin, DTU Danchip, 2014.