Specific Process Knowledge/Etch/Etching of Silicon Oxide/SiO2 etch using AOE/Standard recipe with resist mask/Striation: Difference between revisions

< Specific Process Knowledge | Etch | Etching of Silicon Oxide | SiO2 etch using AOE | Standard recipe with resist mask

Jump to navigation

Jump to search

| Line 18: | Line 18: | ||

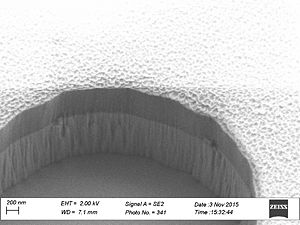

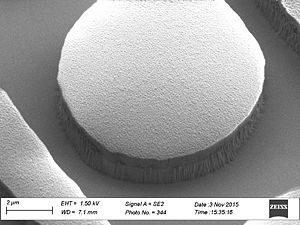

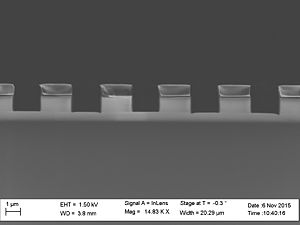

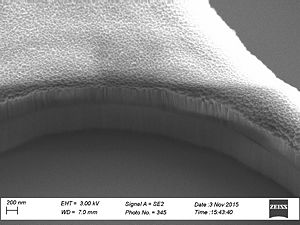

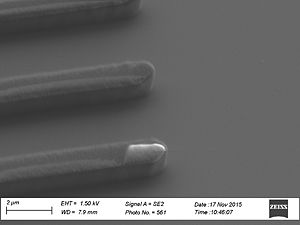

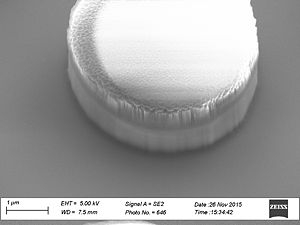

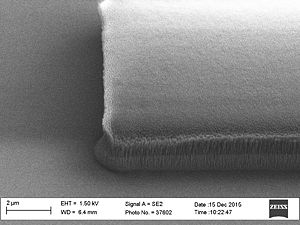

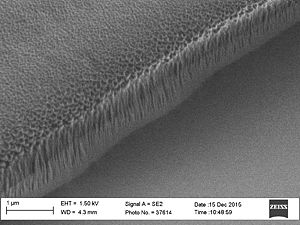

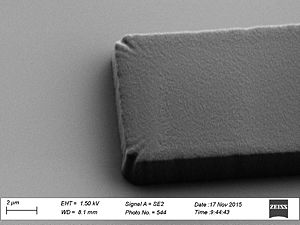

#* SEM: to visually see the SiO2 sidewall roughness and how the resist looks after etch. This only gives a qualitative characterization. [[Specific_Process_Knowledge/Etch/Etching_of_Silicon_Oxide/SiO2_etch_using_AOE/Standard_recipe_with_resist_mask/Striation#Sidewall_roughness_and_resist_surface_after_AOE_etch_viewed_with_SEM_for_the_three_resists:_AZ5214E.2C_AZ_nLof_and_AZ_MIR |See HERE]] | #* SEM: to visually see the SiO2 sidewall roughness and how the resist looks after etch. This only gives a qualitative characterization. [[Specific_Process_Knowledge/Etch/Etching_of_Silicon_Oxide/SiO2_etch_using_AOE/Standard_recipe_with_resist_mask/Striation#Sidewall_roughness_and_resist_surface_after_AOE_etch_viewed_with_SEM_for_the_three_resists:_AZ5214E.2C_AZ_nLof_and_AZ_MIR |See HERE]] | ||

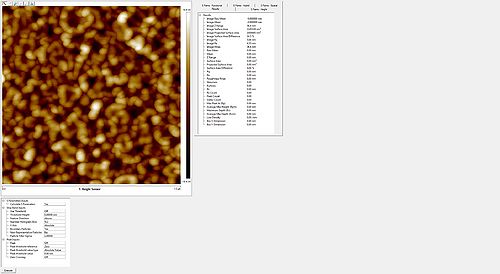

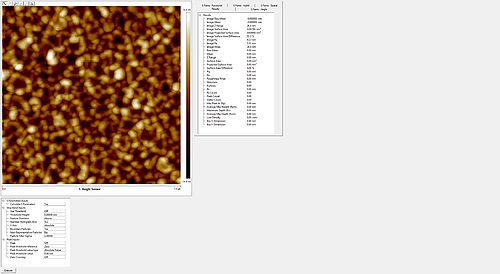

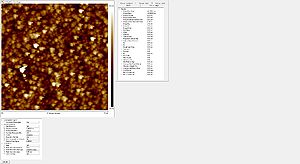

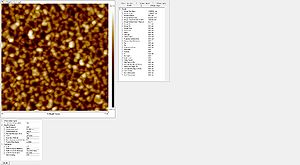

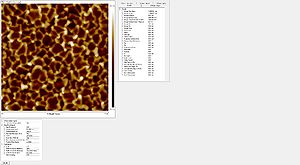

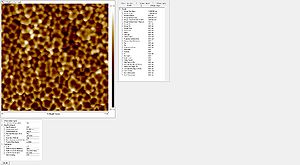

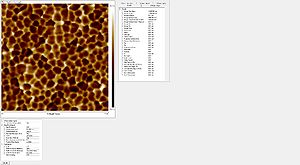

#* AFM: to get at quantitative value for the resist roughness after the etch. I have seem in the literature that this measure reflects the sidewall roughness of the resist. [[Specific_Process_Knowledge/Etch/Etching_of_Silicon_Oxide/SiO2_etch_using_AOE/Standard_recipe_with_resist_mask/Striation#Roughness_of_the_resist_after_AOE_etch_measured_with_the_AFM_of_the_three_resists:_AZ5214E.2C_AZ_nLof_and_AZ_MIR |See HERE]] | #* AFM: to get at quantitative value for the resist roughness after the etch. I have seem in the literature that this measure reflects the sidewall roughness of the resist. [[Specific_Process_Knowledge/Etch/Etching_of_Silicon_Oxide/SiO2_etch_using_AOE/Standard_recipe_with_resist_mask/Striation#Roughness_of_the_resist_after_AOE_etch_measured_with_the_AFM_of_the_three_resists:_AZ5214E.2C_AZ_nLof_and_AZ_MIR |See HERE]] | ||

# Second we tried to toughen the resist by cross linking (by UV flood exposure after development) and heat treatment. Heat treatment at 110 degrees to effectuate the cross linking and heat treatment at 150 degrees to further out-gas and harden the resist. This was only done to AZ5214E and AZ nLof as AZ MIR? Resuslt for the AZ nLof resist: [[Specific_Process_Knowledge/Etch/Etching_of_Silicon_Oxide/SiO2_etch_using_AOE/Standard_recipe_with_resist_mask/Striation#Sidewall_roughness.2Fresist_surface_roughness_effected_by_UV_curing_and_heat_treatment_of_nLof_resist |See HERE]]. Results for the AZ5214E See HERE | # Second we tried to toughen the resist by cross linking (by UV flood exposure after development) and heat treatment. Heat treatment at 110 degrees to effectuate the cross linking and heat treatment at 150 degrees to further out-gas and harden the resist. This was only done to AZ5214E and AZ nLof as AZ MIR? Resuslt for the AZ nLof resist: [[Specific_Process_Knowledge/Etch/Etching_of_Silicon_Oxide/SiO2_etch_using_AOE/Standard_recipe_with_resist_mask/Striation#Sidewall_roughness.2Fresist_surface_roughness_effected_by_UV_curing_and_heat_treatment_of_nLof_resist |See HERE]]. Results for the AZ5214E [[Specific_Process_Knowledge/Etch/Etching_of_Silicon_Oxide/SiO2_etch_using_AOE/Standard_recipe_with_resist_mask/Striation#Sidewall_roughness.2Fresist_surface_roughness_effected_by_UV_curing_and_heat_treatment_of_AZ5214E_resist | See HERE]] | ||

<br clear="all"/> | <br clear="all"/> | ||

Revision as of 09:59, 20 April 2016

Feedback to this page: click here

Striation: Side wall roughness

When etching silicon oxide rough sidewalls are most often seem. This effect is called striation, because it creates stripes along the etched profile. The literature gives several explanations for this. The two main courses seems to be:

- deposition on the sidewalls as the etch proceeds, coursing masking effects

- This can come from flour-carbon polymers from the plasma (some this this layer protects from striation)

- Re-deposition of sputtered SiO2

- damage of the resist mask coursed by plasma heating and/or interaction with the resist. This pattern change at the edge gets transferred to the oxide profile during the etch.

- Resist edge gets rough during etching due to plasma heating (out-gassing while the surface get UV hardened. This make the resist crumple).

- The edge can maybe also get roughened due to sputtering.

This work is focused on trying to improve the resist to avoid the resist damage during etching. From a previous test it has been seen that pre baking the resist AZ1452e at 150 degrees for 5 min can prevent the crumpling of the resist, See results HERE. However this makes the resist flow so the edge profile will not remain vertical.

- First I characterized how our present three standard resists (AZ5214E, AZ nLof and AZ Mir) looked after an SiO2 etch in the AOE (recipe: SiO2_mres). The characterization was done by

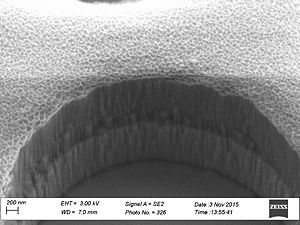

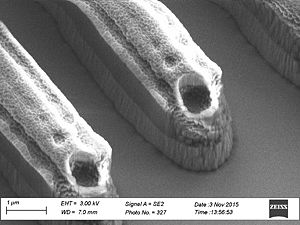

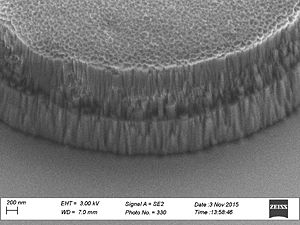

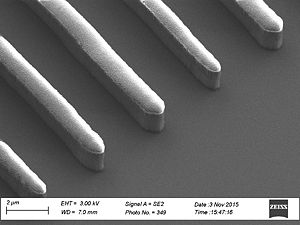

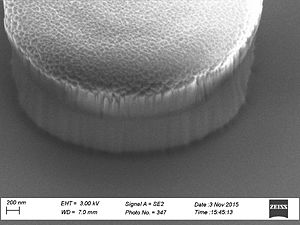

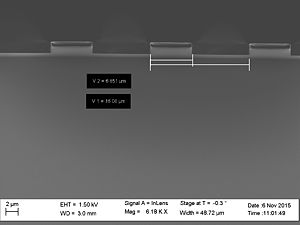

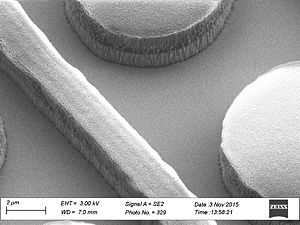

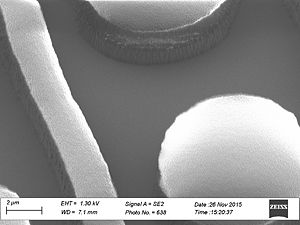

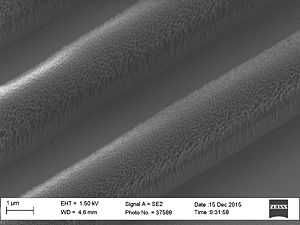

- SEM: to visually see the SiO2 sidewall roughness and how the resist looks after etch. This only gives a qualitative characterization. See HERE

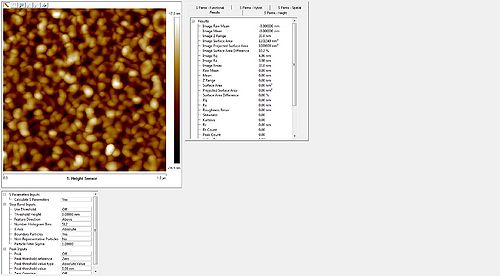

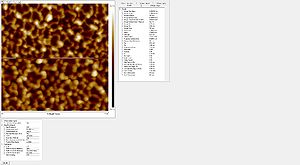

- AFM: to get at quantitative value for the resist roughness after the etch. I have seem in the literature that this measure reflects the sidewall roughness of the resist. See HERE

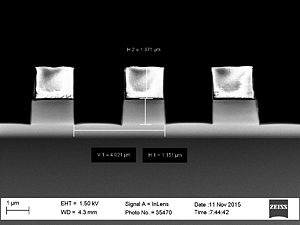

- Second we tried to toughen the resist by cross linking (by UV flood exposure after development) and heat treatment. Heat treatment at 110 degrees to effectuate the cross linking and heat treatment at 150 degrees to further out-gas and harden the resist. This was only done to AZ5214E and AZ nLof as AZ MIR? Resuslt for the AZ nLof resist: See HERE. Results for the AZ5214E See HERE

Sidewall roughness and resist surface after AOE etch viewed with SEM for the three resists: AZ5214E, AZ nLof and AZ MIR

- Striation with different resists used

Roughness of the resist after AOE etch measured with the AFM of the three resists: AZ5214E, AZ nLof and AZ MIR