Specific Process Knowledge/Etch/Etching of Silicon Oxide/SiO2 etch using ASE/tests CHF3+H2: Difference between revisions

Jump to navigation

Jump to search

| (34 intermediate revisions by the same user not shown) | |||

| Line 241: | Line 241: | ||

<br clear="all" /> | <br clear="all" /> | ||

=SiO2 test - 5 jan 2024= | |||

* The SiO2 layer deposited was 2um, deposited on the C1 furnace (recipe: WET1100, 12h40+00:20). | |||

* They were patterned with 915 UVN resist (DUV negative) and 65nm of BARC. | |||

* The following results were processed on chips (2*2cm) bonded to a 100mm dummy wafer. | |||

<br> | |||

{| border="1" cellspacing="1" cellpadding="1" | |||

! '''Recipe''' | |||

! '''Time (min)''' | |||

! '''Date''' | |||

! '''SEM picture''' | |||

! '''Etch rate SiO2 (nm/min)''' | |||

! '''Etch rate resist (nm/min)''' | |||

! '''Selectivity <br> (SiO2:resist)''' | |||

|- | |||

|- | |||

|-style="background:white; color:black" | |||

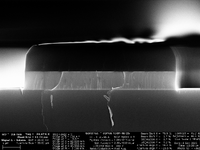

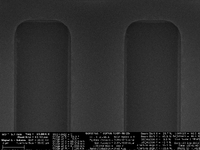

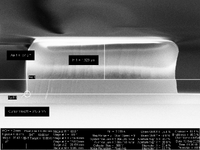

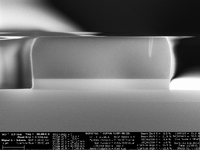

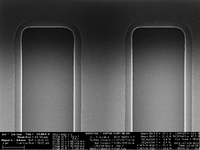

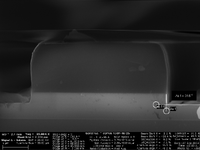

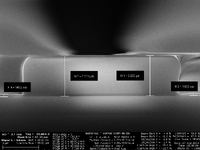

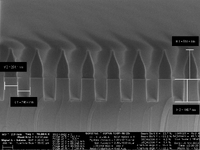

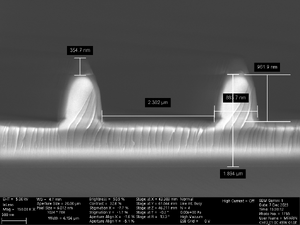

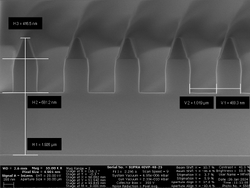

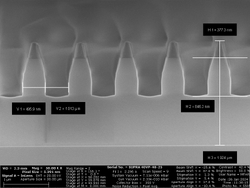

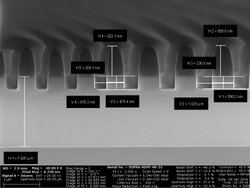

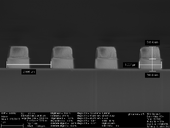

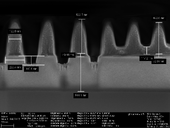

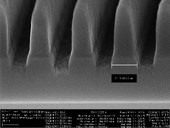

|<!-- '''Recipe name''' --> '''CHF3_t1'''<br> CHF<sub>3</sub>= 22.5 sccm <br> H<sub>2</sub>= 22.5 sccm <br> Coil= 800W <br> Platen= '''30W''' <br> Press= 2.5mTorr <br> Temp= 20°C <br> | |||

|<!--Process time--> 10:00 | |||

|<!--'''Date'''--> 25/01 <br>-2024 | |||

|<!--'''SEM picture'''--> [[File:25.01 CHF3.t1 30w 10m-01.png|250px]] [[File:25.01 CHF3.t1 30w 10m-02.png|250px]] [[File:25.01 CHF3.t1 30w 10m-03.png|250px]] [[File:25.01 CHF3.t1 30w 10m-04.png|250px]] | |||

|<!--'''Etch rate in SiO2'''--> 250nm- 61,99 <br> <br> 500nm- 68,12 <br> <br> 1000nm- 74,7 <br> <br> 2000nm- 76,55 | |||

|<!--'''Etch rate in resist'''--> 250nm- 61,31 <br> <br> 500nm- 49,85 <br> <br> 1000nm- 46,83 <br> <br> 2000nm- 47,3 | |||

|<!--'''Selectivity (SiO2:resist)'''--> 250nm- 1,01 <br> <br> 500nm- 1,37 <br> <br> 1000nm- 1,6 <br> <br> 2000nm- 1,62 | |||

|- | |||

|- | |||

|-style="background:white; color:black" | |||

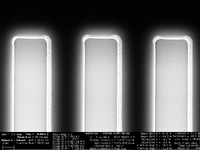

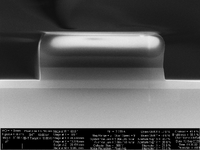

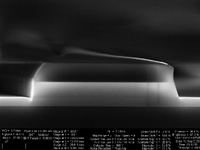

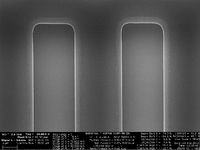

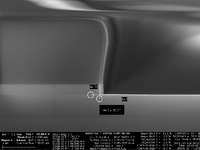

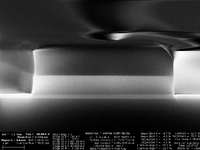

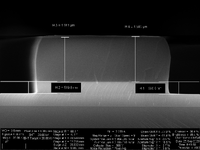

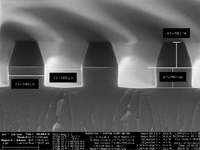

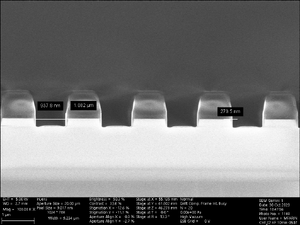

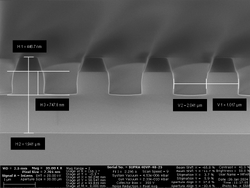

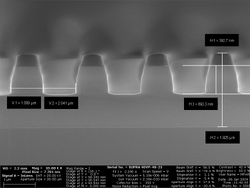

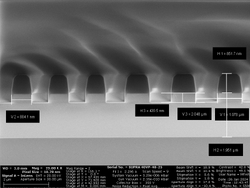

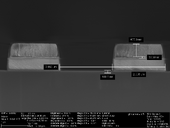

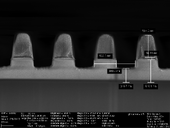

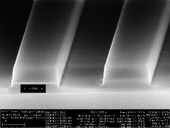

|<!-- '''Recipe name''' --> '''CHF3_t1''' <br> CHF<sub>3</sub>= 22.5 sccm <br> H<sub>2</sub>= 22.5 sccm <br> Coil= 150W <br> Platen= '''45W''' <br> Press= 2.5mTorr <br> Temp= 20°C <br> | |||

|<!--'''Process time'''--> 10:00 | |||

|<!--'''Date'''--> 25/01<br>-2024 | |||

|<!--'''SEM picture'''--> [[File:25.01 CHF3.t1 45w 10m-02.png|250px]] [[File:25.01 CHF3.t1 45w 10m-03.png|250px]] [[File:25.01 CHF3.t1 45w 10m-04.png|250px]] [[File:25.01 CHF3.t1 45w 10m-05.png|250px]] | |||

|<!--'''Etch rate in SiO2'''--> 250nm- 90,74 <br> <br> 500nm- 84,63 <br> <br> 1000nm- 89,33 <br> <br> 2000nm- 94,34 | |||

|<!--'''Etch rate in resist'''--> 250nm- 81,1 <br> <br> 500nm- 53,77 <br> <br> 1000nm- 52,23 <br> <br> 2000nm- 54,81 | |||

|<!--'''Selectivity (SiO2:resist)'''--> 250nm- 1,12 <br> <br> 500nm- 1,57 <br> <br> 1000nm- 1,71 <br> <br> 2000nm- 1,72 | |||

|- | |||

|- | |||

|-style="background:white; color:black" | |||

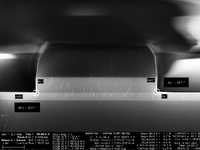

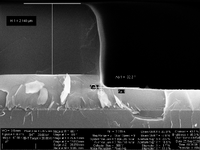

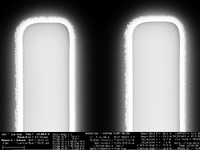

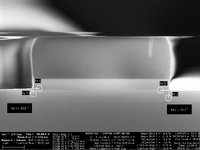

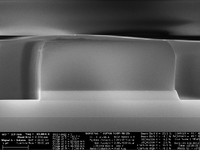

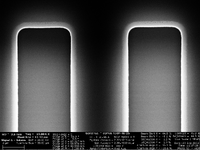

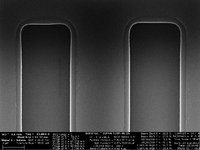

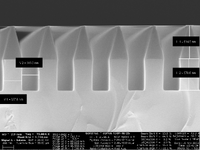

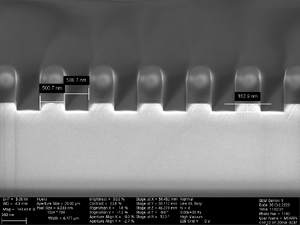

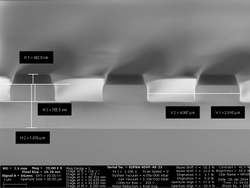

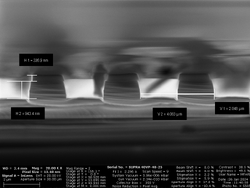

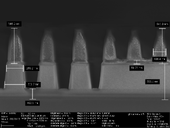

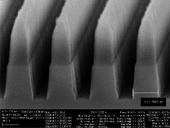

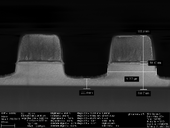

|<!-- '''Recipe name''' --> '''CHF3_t2''' <br> CF<sub>4</sub>= 22.5 sccm <br> H<sub>2</sub>= 22.5 sccm <br> Coil= 150W <br> Platen= '''45W''' <br> Press= 2.5mTorr <br> Temp= 20°C <br> | |||

|<!--'''Process time'''--> 15:00 | |||

|<!--'''Date'''--> 25/01<br>-2024 | |||

|<!--'''SEM picture'''--> [[File:25.01 CHF3.t2 45w 15m-01.png|250px]] [[File:25.01 CHF3.t2 45w 15m-02.png|250px]] [[File:25.01 CHF3.t2 45w 15m-03.png|250px]] [[File:25.01-CHF3.t2-45w-15m-04.png|250px]] <br> *it's visible that redeposits, so the ER and selectivity may not be correct. | |||

|<!--'''Etch rate in SiO2'''-->250nm- 9,18 <br> <br>500nm- 22,46 <br> <br>1000nm- 28,03 <br> <br>2000nm- 28,75 | |||

|<!--'''Etch rate in resist'''-->250nm- 11,09 <br> <br>500nm- 3,96 <br> <br>1000nm- 4,22 <br> <br>2000nm- 4,40 | |||

|<!--'''Selectivity (SiO2:resist)'''-->250nm- 0,83 <br> <br>500nm- 5,67 <br> <br>1000nm- 6,64 <br> <br>2000nm- 6,5 | |||

|- | |||

|- | |||

|} | |||

<br> | |||

<br clear="all" /> | |||

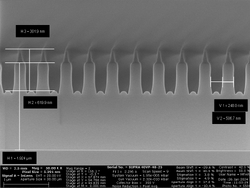

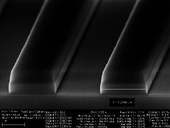

=Etch test of Silicon Nitride= | =Etch test of Silicon Nitride= | ||

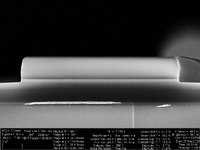

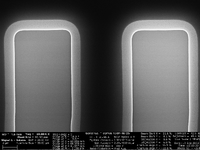

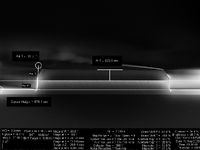

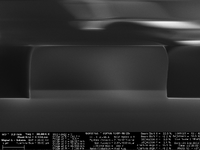

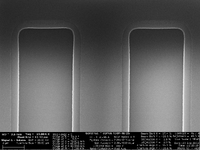

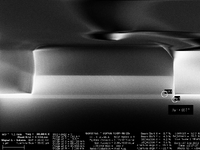

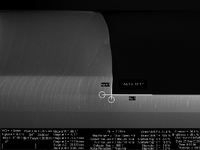

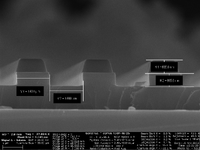

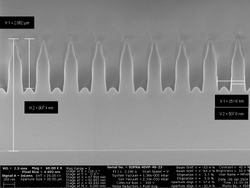

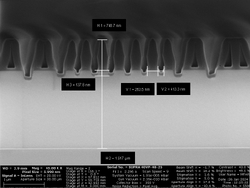

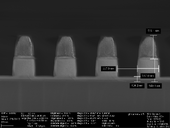

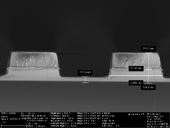

* The nitride layer deposited was 560nm, on the PECVD4 (recipe: Standard HF SiN with wafer clean, for 1h). <br> | |||

* They were patterned with 750 DUV resist and 65nm of BARC (exposure:355 J/m2, focus:-3.1). <br> | |||

* The following results were processed on chips (2*2cm) bonded to a 100mm dummy wafer. | |||

{| border="1" cellspacing="1" cellpadding="1" | {| border="1" cellspacing="1" cellpadding="1" | ||

| Line 276: | Line 334: | ||

|<!--'''Etch rate in resist'''--> 250nm- 23,26 <br> <br> 500nm- 22,60 <br> <br> 1000nm- 16,74 <br> <br> 2000nm- 15,34 | |<!--'''Etch rate in resist'''--> 250nm- 23,26 <br> <br> 500nm- 22,60 <br> <br> 1000nm- 16,74 <br> <br> 2000nm- 15,34 | ||

|<!--'''Selectivity (SiO2:resist)'''--> 250nm- 1.21 <br> <br> 500nm- 1.85 <br> <br> 1000nm- 3.94 <br> <br> 2000nm- 4.15 | |<!--'''Selectivity (SiO2:resist)'''--> 250nm- 1.21 <br> <br> 500nm- 1.85 <br> <br> 1000nm- 3.94 <br> <br> 2000nm- 4.15 | ||

|- | |- | ||

|- | |- | ||

Latest revision as of 12:37, 29 April 2024

Tests performed with UV resist:

The tests were performed on a 100mm wafer patterned on MLA3, with 2.2um AZ5214E resist.

Tests performed with DUV resist:

The resist used was a negative DUV resist (UVN) with 915nm + 88nm BARC layer.

SiO2 test - 5 jan 2024

- The SiO2 layer deposited was 2um, deposited on the C1 furnace (recipe: WET1100, 12h40+00:20).

- They were patterned with 915 UVN resist (DUV negative) and 65nm of BARC.

- The following results were processed on chips (2*2cm) bonded to a 100mm dummy wafer.

Etch test of Silicon Nitride

- The nitride layer deposited was 560nm, on the PECVD4 (recipe: Standard HF SiN with wafer clean, for 1h).

- They were patterned with 750 DUV resist and 65nm of BARC (exposure:355 J/m2, focus:-3.1).

- The following results were processed on chips (2*2cm) bonded to a 100mm dummy wafer.