Specific Process Knowledge/Etch/Etching of Silicon Oxide/SiO2 etch using ASE/tests CHF3+H2: Difference between revisions

Jump to navigation

Jump to search

| (8 intermediate revisions by the same user not shown) | |||

| Line 242: | Line 242: | ||

<br clear="all" /> | <br clear="all" /> | ||

= | =SiO2 test - 5 jan 2024= | ||

* The SiO2 layer deposited was 2um, deposited on the C1 furnace (recipe: WET1100, 12h40+00:20). | |||

* They were patterned with 915 UVN resist (DUV negative) and 65nm of BARC. | |||

* The following results were processed on chips (2*2cm) bonded to a 100mm dummy wafer. | |||

<br> | <br> | ||

| Line 252: | Line 254: | ||

! '''Date''' | ! '''Date''' | ||

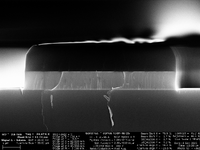

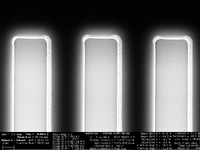

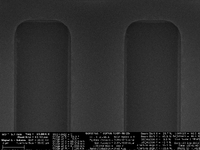

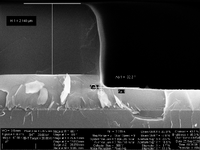

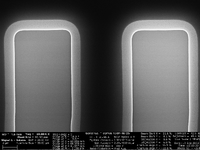

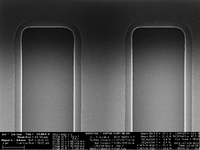

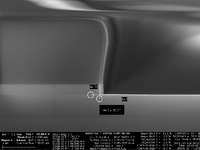

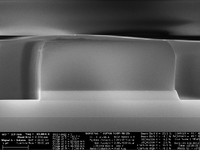

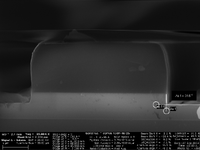

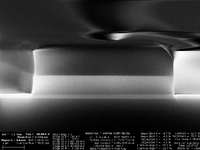

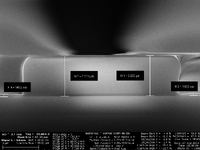

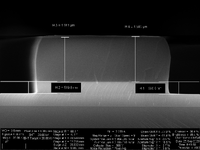

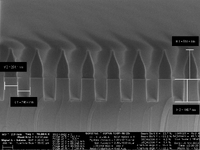

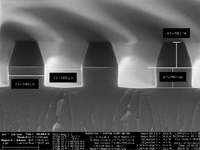

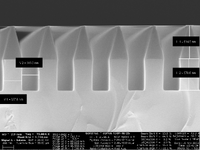

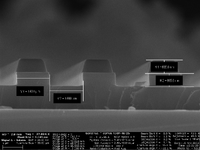

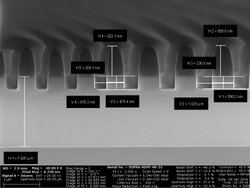

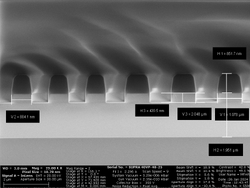

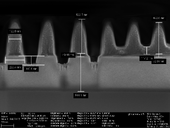

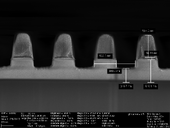

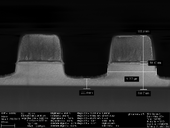

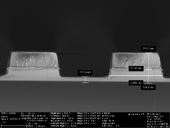

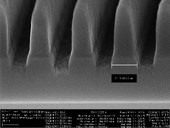

! '''SEM picture''' | ! '''SEM picture''' | ||

! '''Etch rate | ! '''Etch rate SiO2 (nm/min)''' | ||

! '''Etch rate resist (nm/min)''' | ! '''Etch rate resist (nm/min)''' | ||

! '''Selectivity <br> ( | ! '''Selectivity <br> (SiO2:resist)''' | ||

|- | |- | ||

|- | |- | ||

| Line 295: | Line 297: | ||

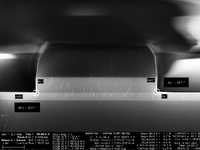

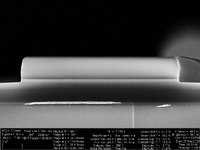

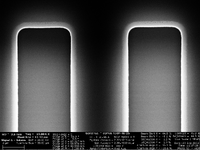

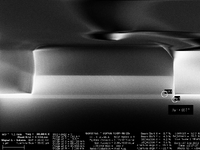

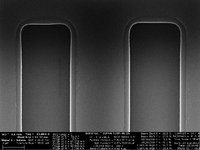

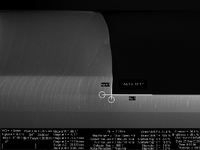

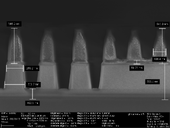

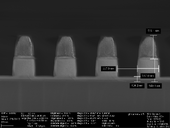

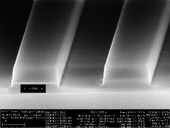

=Etch test of Silicon Nitride= | =Etch test of Silicon Nitride= | ||

* The nitride layer deposited was 560nm, on the PECVD4 (recipe: Standard HF SiN with wafer clean, for 1h). <br> | |||

* They were patterned with 750 DUV resist and 65nm of BARC (exposure:355 J/m2, focus:-3.1). <br> | |||

* The following results were processed on chips (2*2cm) bonded to a 100mm dummy wafer. | |||

{| border="1" cellspacing="1" cellpadding="1" | {| border="1" cellspacing="1" cellpadding="1" | ||

| Line 328: | Line 334: | ||

|<!--'''Etch rate in resist'''--> 250nm- 23,26 <br> <br> 500nm- 22,60 <br> <br> 1000nm- 16,74 <br> <br> 2000nm- 15,34 | |<!--'''Etch rate in resist'''--> 250nm- 23,26 <br> <br> 500nm- 22,60 <br> <br> 1000nm- 16,74 <br> <br> 2000nm- 15,34 | ||

|<!--'''Selectivity (SiO2:resist)'''--> 250nm- 1.21 <br> <br> 500nm- 1.85 <br> <br> 1000nm- 3.94 <br> <br> 2000nm- 4.15 | |<!--'''Selectivity (SiO2:resist)'''--> 250nm- 1.21 <br> <br> 500nm- 1.85 <br> <br> 1000nm- 3.94 <br> <br> 2000nm- 4.15 | ||

|- | |- | ||

|- | |- | ||

Latest revision as of 12:37, 29 April 2024

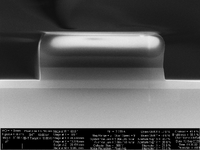

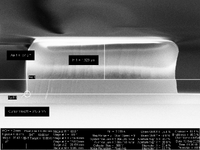

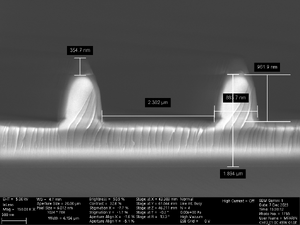

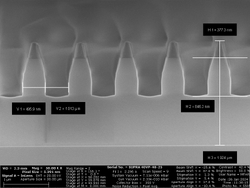

Tests performed with UV resist:

The tests were performed on a 100mm wafer patterned on MLA3, with 2.2um AZ5214E resist.

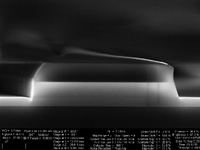

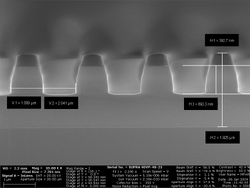

Tests performed with DUV resist:

The resist used was a negative DUV resist (UVN) with 915nm + 88nm BARC layer.

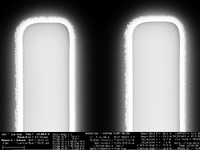

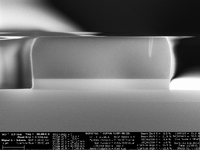

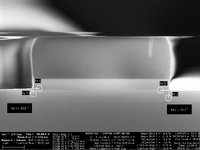

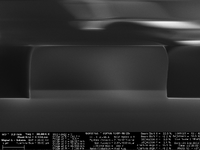

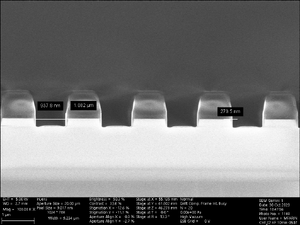

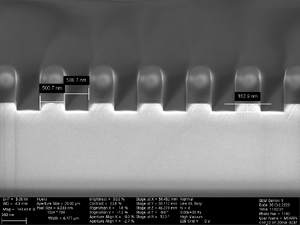

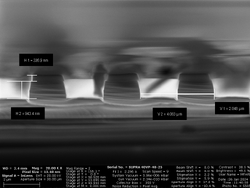

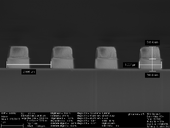

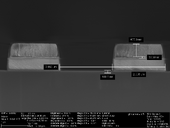

SiO2 test - 5 jan 2024

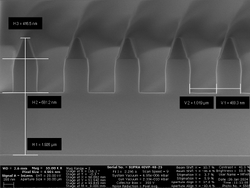

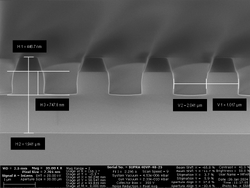

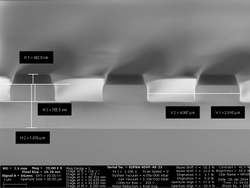

- The SiO2 layer deposited was 2um, deposited on the C1 furnace (recipe: WET1100, 12h40+00:20).

- They were patterned with 915 UVN resist (DUV negative) and 65nm of BARC.

- The following results were processed on chips (2*2cm) bonded to a 100mm dummy wafer.

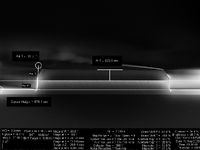

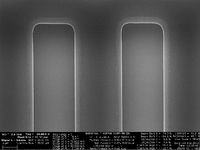

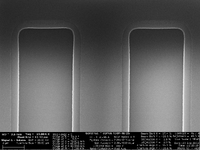

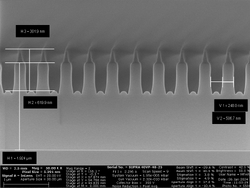

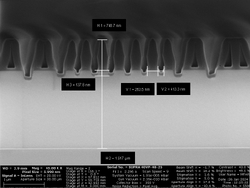

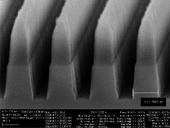

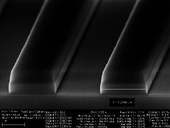

Etch test of Silicon Nitride

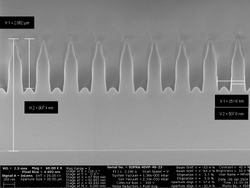

- The nitride layer deposited was 560nm, on the PECVD4 (recipe: Standard HF SiN with wafer clean, for 1h).

- They were patterned with 750 DUV resist and 65nm of BARC (exposure:355 J/m2, focus:-3.1).

- The following results were processed on chips (2*2cm) bonded to a 100mm dummy wafer.