Specific Process Knowledge/Etch/Etching of Silicon Oxide/SiO2 etch using ASE/ICP recipe for SiO2: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

|||

| (45 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

''' ''Unless otherwise stated, all content in this section was done by Maria Farinha@DTU Nanolab, May 2023'' ''' | |||

This recipe was taken from the ICP Metal etch, with a slight difference in the platen temperature. | This recipe was taken from the ICP Metal etch, with a slight difference in the platen temperature. | ||

{| border="1" cellspacing="2" cellpadding="2" | {| border="1" cellspacing="2" cellpadding="2" | ||

|-style="background:Black; color:White" | |-style="background:Black; color:White" | ||

! Parameter | ! Parameter | ||

|Recipe name: ''' | |Recipe name: '''SiO2_ICP''' | ||

|- | |- | ||

|Coil Power [W] | |Coil Power [W] | ||

| | |1000 | ||

|- | |- | ||

|Platen Power [W] | |Platen Power [W] | ||

| | |200 | ||

|- | |- | ||

|Platen temperature [<sup>o</sup>C] | |Platen temperature [<sup>o</sup>C] | ||

|20 | |20 | ||

|- | |- | ||

|C<sub>4</sub>F<sub>8</sub> flow [sccm] | |C<sub>4</sub>F<sub>8</sub> flow [sccm] | ||

|10 | |10 | ||

|- | |- | ||

|H<sub>2</sub> flow [sccm] | |H<sub>2</sub> flow [sccm] | ||

| | |28 | ||

|- | |- | ||

|Pressure [mTorr] | |Pressure [mTorr] | ||

|2.5 | |2.5 | ||

|- | |- | ||

|} | |} | ||

====Results | ====Results with a ''non-patterned wafer''==== | ||

{| border="2" cellspacing="2" cellpadding="3" | {| border="2" cellspacing="2" cellpadding="3" | ||

|-style="background:DarkGray; color:White" | |-style="background:DarkGray; color:White" | ||

! | !Recipe | ||

!Recipe: | !Recipe: SIO2_ICP | ||

! | !SIO2_ICP on stoic Nit | ||

! | !SIO2_ICP on low-stress Nit | ||

|- | |- | ||

|Etch rate | |Etch rate | ||

| | |121 nm/min | ||

(18.07.2023 mfarin @ DTU nanolab) | |||

|194 nm/min | |||

(24.05.2023 mfarin @ DTU nanolab) | |||

|190 nm/min | |||

(24.05.2023 mfarin @ DTU nanolab) | |||

| | |||

| | |||

|- | |- | ||

|} | |} | ||

====Results with a ''patterned wafer'' ==== | |||

====Results | |||

{| border="2" cellspacing="2" cellpadding="3" | {| border="2" cellspacing="2" cellpadding="3" | ||

| Line 128: | Line 55: | ||

!Material to be etched | !Material to be etched | ||

!Recipe: SIO2_ICP | !Recipe: SIO2_ICP | ||

! | !SIO2_ICP on stoic Nit | ||

!SIO2_ICP on low-stress Nit | |||

!SIO2_ICP on Si | |||

|- | |- | ||

|Etch rate in SiO2 | |Etch rate in SiO2 | ||

| | |155 nm/min in the center, 125nm/min in the edges | ||

| | (03052023 mfarin @ DTU nanolab) | ||

| | |||

| | |||

| | |||

|- | |- | ||

|Etch rate in | |Etch rate in resist (AZ 5214E) | ||

|108 nm/min in the center, 98nm/min in the edges | |||

(03052023 mfarin @ DTU nanolab) | |||

| | | | ||

| | |||

| | |||

| | |||

| | |||

| | |||

|- | |- | ||

|Selectivity (SiO2:resist) | |Selectivity (SiO2:resist) | ||

|1. | |1.45 | ||

| | | | ||

| | |||

| | |||

|- | |- | ||

| Line 154: | Line 83: | ||

| | | | ||

| | | | ||

| | |||

| | |||

|- | |- | ||

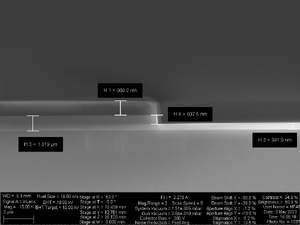

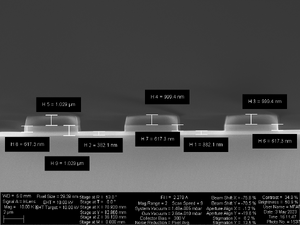

|Profile Images | |Profile Images | ||

|[[File:SiO2_ICP.2-top-02.png|300px]] | |||

[[File:SiO2_ICP.2-top-04.png|300px]] | |||

| | |||

| | | | ||

| | | | ||

|- | |- | ||

|} | |} | ||

*More tests will be done regarding silicon and silicon nitride, since this recipe can be used for overetch. | |||

<br clear="all" /> | <br clear="all" /> | ||

Latest revision as of 15:25, 18 July 2023

Unless otherwise stated, all content in this section was done by Maria Farinha@DTU Nanolab, May 2023

This recipe was taken from the ICP Metal etch, with a slight difference in the platen temperature.

| Parameter | Recipe name: SiO2_ICP |

|---|---|

| Coil Power [W] | 1000 |

| Platen Power [W] | 200 |

| Platen temperature [oC] | 20 |

| C4F8 flow [sccm] | 10 |

| H2 flow [sccm] | 28 |

| Pressure [mTorr] | 2.5 |

Results with a non-patterned wafer

| Recipe | Recipe: SIO2_ICP | SIO2_ICP on stoic Nit | SIO2_ICP on low-stress Nit |

|---|---|---|---|

| Etch rate | 121 nm/min

(18.07.2023 mfarin @ DTU nanolab) |

194 nm/min

(24.05.2023 mfarin @ DTU nanolab) |

190 nm/min

(24.05.2023 mfarin @ DTU nanolab) |

Results with a patterned wafer

- More tests will be done regarding silicon and silicon nitride, since this recipe can be used for overetch.