Specific Process Knowledge/Etch/DRIE-Pegasus/processA/PrA-0: Difference between revisions

Created page with " {| border="2" cellpadding="0" cellspacing="0" style="text-align:center;" |+ '''Process runs''' |- ! rowspan="2" width="40"| Date ! colspan="2" width="120"| Substrate Informa..." |

No edit summary |

||

| (8 intermediate revisions by the same user not shown) | |||

| Line 1: | Line 1: | ||

'''Feedback to this page''': '''[mailto:labadviser@nanolab.dtu.dk?Subject=Feed%20back%20from%20page%20http://labadviser.nanolab.dtu.dk/index.php/Specific_Process_Knowledge/Etch/DRIE-Pegasus/processA/PrA-0 click here]''' | |||

<!--Checked for updates on 30/7-2018 - ok/jmli --> | |||

<!--Checked for updates on 5/10-2020 - ok/jmli --> | |||

<!--Checked for updates on 28/6-2023 - ok/jmli --> | |||

{{contentbydryetch}} | |||

{| border="2" cellpadding="0" cellspacing="0" style="text-align:center;" | {| border="2" cellpadding="0" cellspacing="0" style="text-align:center;" | ||

| Line 7: | Line 13: | ||

! colspan="2" width="120"| Substrate Information | ! colspan="2" width="120"| Substrate Information | ||

! colspan="3" | Process Information | ! colspan="3" | Process Information | ||

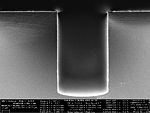

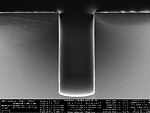

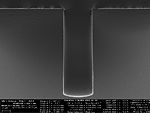

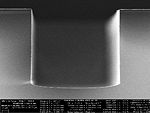

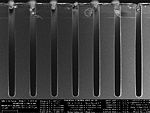

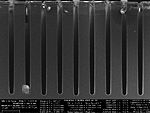

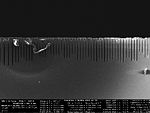

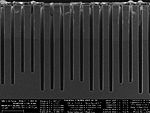

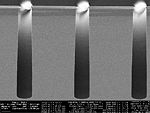

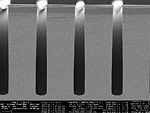

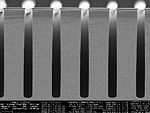

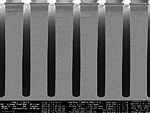

! rowspan="2 | ! rowspan="2" |SEM Images | ||

|- | |- | ||

! width="30" | Wafer info | ! width="30" | Wafer info | ||

! width="40" | | ! width="40" | Exposed area | ||

! width="40" | Conditioning | ! width="40" | Conditioning | ||

! width="40" | Recipe | ! width="40" | Recipe | ||

! width="40" | Wafer ID | ! width="40" | Wafer ID | ||

|- | |- | ||

| | | 2/5-2016 | ||

| 4" | | 4" Travka20 Wafer | ||

| | | 20 % Si | ||

| | | 3 minute TDESC clean | ||

| | | PrA-0, 80 cycles or 14:40 minutes | ||

| | | C03991.01 | ||

| | | | ||

| | [[file:C03991.01 064.jpg|150px|frameless ]] | ||

[[file:C03991.01 065.jpg|150px|frameless ]] | |||

[[file:C03991.01 066.jpg|150px|frameless ]] | |||

[[file:C03991.01 067.jpg|150px|frameless ]] | |||

[[file:C03991.01 068.jpg|150px|frameless ]] | |||

[[file:C03991.01 069.jpg|150px|frameless ]] | |||

[[file:C03991.01 070.jpg|150px|frameless ]] | |||

[[file:C03991.01 071.jpg|150px|frameless ]] | |||

[[file:C03991.01 072.jpg|150px|frameless ]] | |||

[[file:C03991.01 073.jpg|150px|frameless ]] | |||

[[file:C03991.01 074.jpg|150px|frameless ]] | |||

[[file:C03991.01 075.jpg|150px|frameless ]] | |||

[[file:C03991.01 076.jpg|150px|frameless ]] | |||

[[file:C03991.01 077.jpg|150px|frameless ]] | |||

[[file:C03991.01 078.jpg|150px|frameless ]] | |||

[[file:C03991.01 079.jpg|150px|frameless ]] | |||

[[file:C03991.01 080.jpg|150px|frameless ]] | |||

[[file:C03991.01 081.jpg|150px|frameless ]] | |||

[[file:C03991.01 101.jpg|150px|frameless ]] | |||

|- | |||

| 2/5-2016 | |||

| 4" Travka20 Wafer | |||

| 20 % Si | |||

| 3 minute TDESC clean | |||

| PrA-0, 80 cycles or 14:40 minutes | |||

| C03991.04 | |||

| | |||

[[file:C03991.04 120.jpg|150px|frameless ]] | |||

[[file:C03991.04 121.jpg|150px|frameless ]] | |||

[[file:C03991.04 122.jpg|150px|frameless ]] | |||

[[file:C03991.04 123.jpg|150px|frameless ]] | |||

[[file:C03991.04 124.jpg|150px|frameless ]] | |||

[[file:C03991.04 125.jpg|150px|frameless ]] | |||

[[file:C03991.04 126.jpg|150px|frameless ]] | |||

[[file:C03991.04 127.jpg|150px|frameless ]] | |||

[[file:C03991.04 128.jpg|150px|frameless ]] | |||

[[file:C03991.04 129.jpg|150px|frameless ]] | |||

[[file:C03991.04 130.jpg|150px|frameless ]] | |||

[[file:C03991.04 131.jpg|150px|frameless ]] | |||

[[file:C03991.04 132.jpg|150px|frameless ]] | |||

[[file:C03991.04 133.jpg|150px|frameless ]] | |||

[[file:C03991.04 134.jpg|150px|frameless ]] | |||

[[file:C03991.04 135.jpg|150px|frameless ]] | |||

[[file:C03991.04 136.jpg|150px|frameless ]] | |||

|- | |||

| 3/6-2016 | |||

| 4" Travka20 Wafer | |||

| 20 % Si | |||

| 3 minute TDESC clean | |||

| PrA-0, 80 cycles or 14:40 minutes | |||

| C04047.01 | |||

| | |||

[[file:C04047.01 081.jpg|150px|frameless ]] | |||

[[file:C04047.01 082.jpg|150px|frameless ]] | |||

[[file:C04047.01 080.jpg|150px|frameless ]] | |||

[[file:C04047.01 079.jpg|150px|frameless ]] | |||

[[file:C04047.01 078.jpg|150px|frameless ]] | |||

[[file:C04047.01 077.jpg|150px|frameless ]] | |||

[[file:C04047.01 076.jpg|150px|frameless ]] | |||

[[file:C04047.01 075.jpg|150px|frameless ]] | |||

[[file:C04047.01 074.jpg|150px|frameless ]] | |||

[[file:C04047.01 073.jpg|150px|frameless ]] | |||

[[file:C04047.01 072.jpg|150px|frameless ]] | |||

[[file:C04047.01 071.jpg|150px|frameless ]] | |||

[[file:C04047.01 070.jpg|150px|frameless ]] | |||

|- | |||

| 3/6-2016 | |||

| 4" Travka20 Wafer | |||

| 20 % Si | |||

| 3 minute TDESC clean | |||

| PrA-0, 80 cycles or 14:40 minutes | |||

| C04047.04 | |||

| | | | ||

[[file: | [[file:C04047.04 110.jpg|150px|frameless ]] | ||

[[file: | [[file:C04047.04 111.jpg|150px|frameless ]] | ||

[[file: | [[file:C04047.04 112.jpg|150px|frameless ]] | ||

[[file: | [[file:C04047.04 113.jpg|150px|frameless ]] | ||

[[file: | [[file:C04047.04 114.jpg|150px|frameless ]] | ||

[[file: | [[file:C04047.04 115.jpg|150px|frameless ]] | ||

[[file: | [[file:C04047.04 116.jpg|150px|frameless ]] | ||

[[file:C04047.04 117.jpg|150px|frameless ]] | |||

[[file:C04047.04 118.jpg|150px|frameless ]] | |||

[[file:C04047.04 119.jpg|150px|frameless ]] | |||

[[file:C04047.04 120.jpg|150px|frameless ]] | |||

[[file:C04047.04 121.jpg|150px|frameless ]] | |||

[[file:C04047.04 122.jpg|150px|frameless ]] | |||

[[file:C04047.04 123.jpg|150px|frameless ]] | |||

|- | |- | ||

|} | |} | ||

Latest revision as of 11:32, 28 June 2023

Feedback to this page: click here

Unless otherwise stated, the content of this page was created by the dry etch group at DTU Nanolab

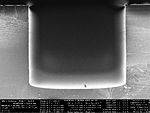

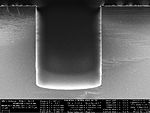

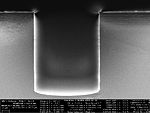

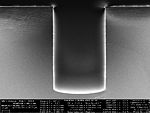

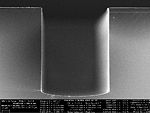

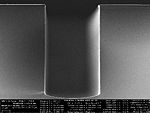

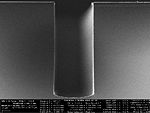

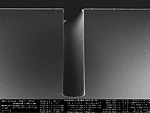

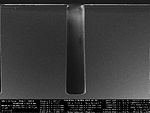

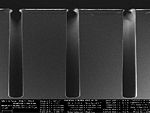

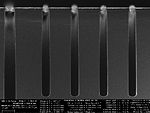

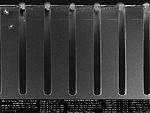

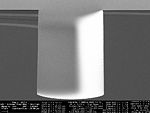

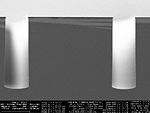

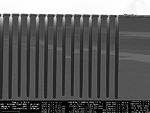

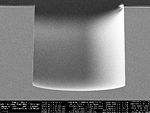

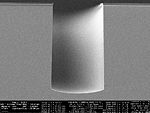

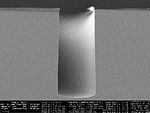

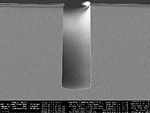

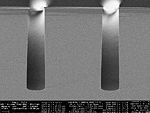

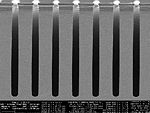

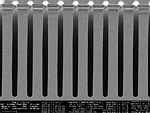

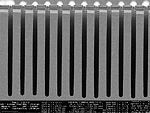

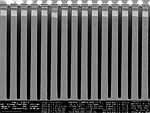

| Date | Substrate Information | Process Information | SEM Images | |||

|---|---|---|---|---|---|---|

| Wafer info | Exposed area | Conditioning | Recipe | Wafer ID | ||

| 2/5-2016 | 4" Travka20 Wafer | 20 % Si | 3 minute TDESC clean | PrA-0, 80 cycles or 14:40 minutes | C03991.01 | |

| 2/5-2016 | 4" Travka20 Wafer | 20 % Si | 3 minute TDESC clean | PrA-0, 80 cycles or 14:40 minutes | C03991.04 | |

| 3/6-2016 | 4" Travka20 Wafer | 20 % Si | 3 minute TDESC clean | PrA-0, 80 cycles or 14:40 minutes | C04047.01 | |

| 3/6-2016 | 4" Travka20 Wafer | 20 % Si | 3 minute TDESC clean | PrA-0, 80 cycles or 14:40 minutes | C04047.04 | |