Specific Process Knowledge/Etch/Etching of Silicon Oxide/SiO2 etch using RIE1 or RIE2/Images of 1SIO2mbr with burned resist mask: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

No edit summary |

||

| Line 1: | Line 1: | ||

'''Feedback to this page''': '''[mailto:labadviser@ | '''Feedback to this page''': '''[mailto:labadviser@nanolab.dtu.dk?Subject=Feed%20back%20from%20page%20http://labadviser.nanolab.dtu.dk/index.php/Specific_Process_Knowledge/Etch/Etching_of_Silicon_Oxide/SiO2_etch_using_RIE1_or_RIE2/Images_of_1SIO2mbr_with_burned_resist_mask click here]''' | ||

=<span style="color:#FF0000"> Both RIE's (RIE1 and RIE2) for silicon based etching has been decommissioned </span> = | =<span style="color:#FF0000"> Both RIE's (RIE1 and RIE2) for silicon based etching has been decommissioned </span> = | ||

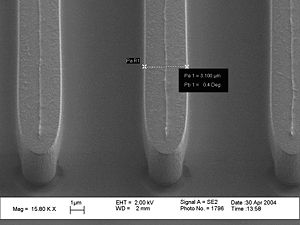

===Etch of SiO2 using the recipe 1SIO2mbr with burned resist as masking material === | ===Etch of SiO2 using the recipe 1SIO2mbr with burned resist as masking material === | ||

''Berit Geilman Herstrøm (BGE) from | ''Berit Geilman Herstrøm (BGE) from Nanolab@DTU'' | ||

{| border="2" cellspacing="1" cellpadding="3" align="left" | {| border="2" cellspacing="1" cellpadding="3" align="left" | ||

Revision as of 17:24, 25 November 2019

Feedback to this page: click here

Both RIE's (RIE1 and RIE2) for silicon based etching has been decommissioned

Etch of SiO2 using the recipe 1SIO2mbr with burned resist as masking material

Berit Geilman Herstrøm (BGE) from Nanolab@DTU