Specific Process Knowledge/Thermal Process/Dope with Phosphorus: Difference between revisions

No edit summary |

No edit summary |

||

| Line 2: | Line 2: | ||

The Phosphorus Predep furnace (A4) can be used for predeposition of silicon wafers | The Phosphorus Predep furnace (A4) can be used for phosphorus predeposition of silicon wafers, resulting in N-type doping. In the furnace, the silicon wafers are positioned in a quarts boat. | ||

''' | ''' | ||

| Line 11: | Line 11: | ||

''' | ''' | ||

To study the | To study the correlation between the temperature for the predeposition process and drive-in of the phosphorus doping in the Phosphorus Predep furnace (A4) at DTU Danchip. | ||

''' | ''' | ||

| Line 17: | Line 17: | ||

====Experimental setup==== | ====Experimental setup==== | ||

''' | ''' | ||

20 boron doped wafers (p-type) were used - Four wafers for each of the five different predeposition temperatures. In the furnace five dummy wafers were placed on each side of the | 20 boron doped device wafers (p-type) were used - Four wafers for each of the five different predeposition temperatures. In the furnace five dummy wafers were placed on each side of the device wafers. The dummy wafers nearest to the device wafers were changed in-between the runs to miniminze doping from these dummy wafers. | ||

{| border="1" cellspacing="1" cellpadding="2" style="text-align:center;" width="690" ||3||4||5 | {| border="1" cellspacing="1" cellpadding="2" style="text-align:center;" width="690" ||3||4||5 | ||

!| Run #||Temperature||Process time with POCl<sub>3</sub>|| | !| Run #||Temperature||Process time with POCl<sub>3</sub>||Annealing time in N<sub>2</sub>||Wafer # | ||

|- | |- | ||

|1||850 <sup>o</sup>C||15 minutes||20 miuntes||1, 2, 3, 4 | |1||850 <sup>o</sup>C||15 minutes||20 miuntes||1, 2, 3, 4 | ||

| Line 33: | Line 33: | ||

|} | |} | ||

''' | ''' | ||

After the predeposition two wafers from each run were taken out to be further processed. These wafers were: 1, 2, 5, 6, 9, 10, 13, 14, 17, 18. | After the predeposition two wafers from each run were taken out to be further processed. These wafers were: 1, 2, 5, 6, 9, 10, 13, 14, 17, 18. These wafers were dipped in BHF to remove the phosphorus glass layer before the drive-in process. | ||

The drive-in process was made in the Phosphorus Drive-in furnace (A3) for all the mentioned wafers same time. At the drive-in process a dummy wafer was placed in-between the wafers from different temperatures so doping from wafer to wafer was minimized. The drive-in was done with the process "DRY1050" with is a dry oxidation at 1050 <sup>o</sup>C for 100 minutes and 20 minutes annealing. At the oxidation was the O<sub>2</sub> flow was 5 SLM, and the N<sub>2</sub> flow for annealing was 3 SLM. | |||

====Result==== | ====Result==== | ||

| Line 103: | Line 103: | ||

|- | |- | ||

! width="130" | Wafer # | ! width="130" | Wafer # | ||

! width="130" | Temperature [C] | ! width="130" | Temperature [<sup>o</sup>C] | ||

! width="130" | Thinkness [nm] | ! width="130" | Thinkness [nm] | ||

! width="130" | Refrative index | ! width="130" | Refrative index | ||

| Line 163: | Line 163: | ||

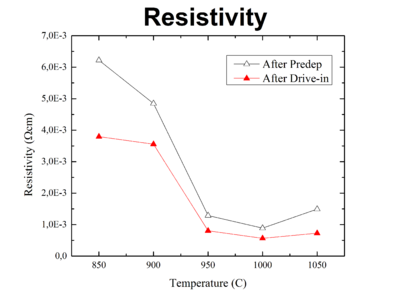

|[[image:Resistivity.png|400x400px|right|thumb|Resistivity]]||[[image:Sheet_resistance.png|400x400px|right|thumb|Sheet resistance]] | |[[image:Resistivity.png|400x400px|right|thumb|Resistivity]]||[[image:Sheet_resistance.png|400x400px|right|thumb|Sheet resistance]] | ||

|- | |- | ||

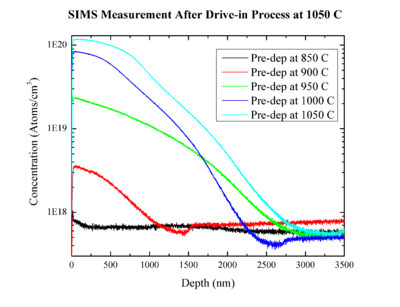

|[[image:SIMS Measurement_After_Pre-dep.png|400x400px|right|thumb|SIMS Measurement After Pre-dep]]||[[image:SIMS Measurement_After_Drive-in_Process_at_1050_C.png|400x400px|right|thumb|SIMS Measurement After Drive-in Process at 1050 C]] | |[[image:SIMS Measurement_After_Pre-dep.png|400x400px|right|thumb|SIMS Measurement After Pre-dep]]||[[image:SIMS Measurement_After_Drive-in_Process_at_1050_C.png|400x400px|right|thumb|SIMS Measurement After Drive-in Process at 1050 <sup>o</sup>C]] | ||

|- | |- | ||

|} | |} | ||

Looking at the 'SIMS Measurement after Drive-in Process at 1050 C | Looking at the 'SIMS Measurement after Drive-in Process at 1050 <sup>o</sup>C it can be seen that 'Pre-dep at 950 <sup>o</sup>C and 'Pre-dep at 1000 <sup>o</sup>C are crossing each other but they should not do that. There have only been meassured on one wafer so there is not that mush statistical data to verify it with. | ||

Revision as of 11:07, 21 October 2013

Feedback to this page: click here

The Phosphorus Predep furnace (A4) can be used for phosphorus predeposition of silicon wafers, resulting in N-type doping. In the furnace, the silicon wafers are positioned in a quarts boat.

Test of the Phosphorus Predep furnace

Purpose

To study the correlation between the temperature for the predeposition process and drive-in of the phosphorus doping in the Phosphorus Predep furnace (A4) at DTU Danchip.

Experimental setup

20 boron doped device wafers (p-type) were used - Four wafers for each of the five different predeposition temperatures. In the furnace five dummy wafers were placed on each side of the device wafers. The dummy wafers nearest to the device wafers were changed in-between the runs to miniminze doping from these dummy wafers.

| Run # | Temperature | Process time with POCl3 | Annealing time in N2 | Wafer # |

|---|---|---|---|---|

| 1 | 850 oC | 15 minutes | 20 miuntes | 1, 2, 3, 4 |

| 2 | 900 oC | 15 minutes | 20 miuntes | 5, 6, 7, 8 |

| 3 | 950 oC | 15 minutes | 20 miuntes | 9, 10, 11, 12 |

| 4 | 1000 oC | 15 minutes | 20 miuntes | 13, 14, 15, 16 |

| 5 | 1050 oC | 15 minutes | 20 miuntes | 17, 18, 19, 20 |

After the predeposition two wafers from each run were taken out to be further processed. These wafers were: 1, 2, 5, 6, 9, 10, 13, 14, 17, 18. These wafers were dipped in BHF to remove the phosphorus glass layer before the drive-in process.

The drive-in process was made in the Phosphorus Drive-in furnace (A3) for all the mentioned wafers same time. At the drive-in process a dummy wafer was placed in-between the wafers from different temperatures so doping from wafer to wafer was minimized. The drive-in was done with the process "DRY1050" with is a dry oxidation at 1050 oC for 100 minutes and 20 minutes annealing. At the oxidation was the O2 flow was 5 SLM, and the N2 flow for annealing was 3 SLM.

Result

Several measurements were done for the different wafers in the process. After the pre-deposition thickness of the Phosphorus glass layer was measured and the sheet resistance and slice resistivity measured on the same wafer after a BHF etch.

| Ellipsometer (center point only) | Four Point Probe | ||||

|---|---|---|---|---|---|

| Wafer # | Temperature [C] | Thinkness [nm] | Refrative index | Sheet resistance [Ωsq] | Slice Resistivity [Ωcm] |

| 3 | 850 | 27,4 | 1,4623 | 311 | 17,32 |

| 7 | 900 | 45,27 | 1,4622 | 138,5 | 7,61 |

| 11 | 950 | 61,36 | 1,4625 | 16,12 | 0,859 |

| 15 | 1000 | 80,45 | 1,4624 | 7,4 | 0,392 |

| 19 | 1050 | 119,37 | 1,4623 | 6,6 | 0,246 |

| Avg. five point on Filmtek | Four Point Probe | ||||

|---|---|---|---|---|---|

| Wafer # | Temperature [oC] | Thinkness [nm] | Refrative index | Sheet resistance [Ωsq] | Slice Resistivity [Ωcm] |

| 2 | 850 | 110,44 | 1,4654 | 189,7 | 13,06 |

| 6 | 900 | 116,28 | 1,4629 | 101,6 | 5,32 |

| 9 | 950 | 137,06 | 1,4604 | 10,05 | 0,527 |

| 14 | 1000 | 141,46 | 1,4651 | 4,72 | 0,216 |

| 18 | 1050 | 139,87 | 1,4659 | 3,23 | 0,165 |

| Test | 110,71 | 1,46286 | - | - | |

Looking at the 'SIMS Measurement after Drive-in Process at 1050 oC it can be seen that 'Pre-dep at 950 oC and 'Pre-dep at 1000 oC are crossing each other but they should not do that. There have only been meassured on one wafer so there is not that mush statistical data to verify it with.