### Diffusion of In<sub>0.53</sub>Ga<sub>0.47</sub>As elements through hafnium oxide during post deposition annealing

Cite as: Appl. Phys. Lett. 104, 011601 (2014); https://doi.org/10.1063/1.4860960 Submitted: 19 March 2013 . Accepted: 15 December 2013 . Published Online: 08 January 2014

W. Cabrera, B. Brennan, H. Dong, T. P. O'Regan, I. M. Povey, S. Monaghan, É. O'Connor, P. K. Hurley, R. M. Wallace, and Y. J. Chabal

ARTICLES YOU MAY BE INTERESTED IN

Indium out-diffusion in Al<sub>2</sub>O<sub>3</sub>/InGaAs stacks during anneal at different ambient conditions Applied Physics Letters 104, 243504 (2014); https://doi.org/10.1063/1.4882645

GaAs interfacial self-cleaning by atomic layer deposition Applied Physics Letters 92, 071901 (2008); https://doi.org/10.1063/1.2883956

Indium outdiffusion and leakage degradation in metal/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As capacitors Applied Physics Letters 103, 053502 (2013); https://doi.org/10.1063/1.4816588

## Diffusion of $In_{0.53}Ga_{0.47}As$ elements through hafnium oxide during post deposition annealing

W. Cabrera, <sup>1</sup> B. Brennan, <sup>1</sup> H. Dong, <sup>1</sup> T. P. O'Regan, <sup>2,a)</sup> I. M. Povey, <sup>2</sup> S. Monaghan, <sup>2</sup> É. O'Connor, <sup>2</sup> P. K. Hurley, <sup>2</sup> R. M. Wallace, <sup>1</sup> and Y. J. Chabal <sup>1,b)</sup>

<sup>1</sup>Department of Materials Science and Engineering, University of Texas at Dallas, Richardson, Texas 75080, USA

<sup>2</sup>Tyndall National Institute, University College Cork, Lee Maltings, Prospect Row, Cork, Ireland

(Received 19 March 2013; accepted 15 December 2013; published online 8 January 2014)

Diffusion of indium through HfO<sub>2</sub> after post deposition annealing in N<sub>2</sub> or forming gas environments is observed in HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As stacks by low energy ion scattering and X-ray photo electron spectroscopy and found to be consistent with changes in interface layer thickness observed by transmission electron microscopy. Prior to post processing, arsenic oxide is detected at the surface of atomic layer deposition-grown HfO<sub>2</sub> and is desorbed upon annealing at 350 °C. Reduction of the interfacial layer thickness and potential densification of HfO<sub>2</sub>, resulting from indium diffusion upon annealing, is confirmed by an increase in capacitance. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4860960]

Further scaling for high performance devices has fostered the search of a replacement for Si as the active device channel, with considerable attention on high electron mobility III-V compound semiconductors. However, a range of technological challenges need to be resolved before the full potential of III-V channel materials can be realized. There is therefore an active effort to investigate the atomic layer deposition (ALD) and post-deposition processes of high-k dielectrics on III-V substrates to correlate and understand the dependence of electrical properties on the processing conditions.

Wet chemical surface cleaning and pretreatments prior to high-k deposition, <sup>3,4</sup> variation in deposition temperature, <sup>5</sup> and most recently incorporation of III-V barrier layers <sup>6</sup> have all been shown to affect the electrical performance. A "self-cleaning" or "clean-up" phenomenon is believed to lead to reduction of the native oxides initially present on the III-V surfaces during ALD of high-k oxides, particularly using trimethylaluminum (TMA) or tetrakisethylmethylaminohafnium (TEMA-Hf) and water (H<sub>2</sub>O). <sup>7–9</sup> Although this process results in an improvement in the electrical properties of high-k/III-V interfaces, the presence of fixed charges and bulk electron/hole traps in the high-k oxide is still an issue for device performance.

As in the silicon technology, post deposition anneals (PDA) in forming gas (FGA) can improve the electrical characteristics of silicon-based devices by reducing the density of interface states ( $D_{it}$ ). Similarly, electrical measurements have shown that annealing in N<sub>2</sub> and/or FGA can reduce the  $D_{it}$  of high-k/III-V gate stacks.  $^{3,11-14}$  However, the effect of these treatments on the *chemical composition* of the samples has not been fully understood.

It has been suggested, for instance, that PDA could induce changes in interfacial chemical composition due to the thermal instability of the In<sub>0.53</sub>Ga<sub>0.47</sub>As native oxides.<sup>15</sup>

Decomposed elements from the native oxides could diffuse through the high-k dielectric which would lead to electrical instabilities. 16,17 Most recently, using ex-situ hard X-ray photoelectron spectroscopy (XPS), Weiland et al. 18 observed Ga and As out-diffusion on Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As stacks after N<sub>2</sub> annealing at temperatures between 400 °C and 700 °C. In another study, Kang et al. 19 noted Ga-O formation on the top surface on Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/GaAs gate stacks after PDA at 700 °C. All these studies suggest that III-V substrate elements might diffuse completely through the high-k dielectric film after post deposition anneals, although there have been no unambiguous proof and quantification of such diffusion. It is therefore important to devise experiments with tools that can provide clear evidence for elemental diffusion and changes in the chemical composition of high-k/III-V gate stacks for future production of high mobility devices.

In this work, low energy ion scattering (LEIS), XPS, and transmission electron microscopy (TEM) are used to investigate elemental diffusion, to examine the chemical composition of the surface and near-surface region upon PDA of ALD-grown HfO<sub>2</sub> on In<sub>0.53</sub>Ga<sub>0.47</sub>As, and to correlate these phenomena to the thickness of the interfacial layer. Furthermore, capacitance-voltage (C-V) and current-voltage (I-V) measurements are performed to determine the effect of the annealing on the maximum accumulation capacitance and oxide leakage in Pd/HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As gate stacks.

For this study,  $In_{0.53}Ga_{0.47}As$  layers were grown on 50 mm diameter, sulfur-doped InP(100) substrates (doping  $\sim 3$ –8  $\times 10^{18}$  cm $^{-3}$ ). The buffer layer for  $In_{0.53}Ga_{0.47}As$  growth consisted of a 0.1  $\mu$ m thick sulfur-doped InP (doping  $\sim 2 \times 10^{18}$  cm $^{-3}$ ). Both the InP buffer and  $In_{0.53}Ga_{0.47}As$  top epitaxial layers were grown using metal-organic vapor phase epitaxy. The top epitaxial layer of sulfur-doped  $In_{0.53}Ga_{0.47}As$  (doping  $\sim 4 \times 10^{17}$  cm $^{-3}$ ) was 2  $\mu$ m thick. The 4 nm-thick HfO $_2$  films were grown by ALD on the epi-ready  $In_{0.53}Ga_{0.47}As/InP$  wafers at 250 °C, using TEMA-Hf and water pulses with an argon carrier gas operating at approximately 0.1 Torr pressure (base pressure  $< 1 \times 10^{-5}$  Torr). To maximize the change in the electronic and structural

a)Present address: General Technical Services at the ARL, 2800 Powder Mill Road, Adelphi, Maryland 20783, USA.

b)Electronic mail: chabal@utdallas.edu

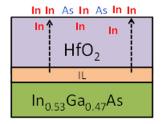

properties of the HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS system following the forming gas anneal, the as-grown sample was not cleaned (used as is) prior to the deposition of the thin HfO<sub>2</sub> layer by ALD. Consequently, there is interfacial oxide layer between the HfO<sub>2</sub> layer and the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface, initially comprised of oxides of indium, gallium, and arsenic.<sup>20</sup> The HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As samples were subjected to three different post deposition treatments in this study: (1) no post-deposition anneal, (2) N<sub>2</sub> anneal (at atmospheric pressure) at 350 °C for 30 min, and (3) FGA (5% H<sub>2</sub>: 95% N<sub>2</sub> at atmospheric pressure) at 350 °C for 30 min. MOS capacitor structures with a range of gate areas were fabricated by e-beam evaporation of a 200 nm Pd gate using a lift-off process. No ohmic back contact was necessary due to the high doping concentration in the InP substrate and the negligible series resistance.

The choice for the annealing temperature and time included the following factors. First, a wide range of post deposition anneal temperatures from 325 to 700 °C had been reported, 3,11,12,14,18,19 with times varying from 60 s to 1 h. Second, for all studies published to date focusing specifically on diffusion of substrate elements, the lowest temperature reported was 400 °C. <sup>18</sup> The temperature of 350 °C was first selected in this study to assess if diffusion would occur at a temperature lower than employed in previous reports. So an anneal temperature and time were selected to coincide with the anneal conditions reported in studies by Long *et al.* <sup>14</sup> Importantly, samples with post deposition anneal at the same temperature and time in FGA (5% H<sub>2</sub>: 95% N<sub>2</sub>) and pure N<sub>2</sub> were studied to explore the role (if any) of H<sub>2</sub> in the ambient during the post deposition anneal.

XPS measurements were performed at a scanning angle of 45° with respect to the sample surface using a monochromated Al K $\alpha$  x-ray source (h $\nu$  = 1486.7 eV) and electron detection with a 7 channel hemispherical analyzer operating at a pass energy of 15 eV in an ultra-high vacuum chamber (base pressure of <5 × 10<sup>-10</sup> mbar), as described in more detail elsewhere. <sup>21</sup> Spectral peak deconvolution was carried out using the Analyzer peak fitting software, which allows for independent control of the Gaussian and Lorentzian peak components, as well as for dynamically fitting the peak background during the fitting process. This procedure provides a much more accurate background subtraction.

LEIS was used to examine the surface composition with high depth resolution for elements such as metal and oxygen.<sup>22</sup> Analysis was performed in a chamber equipped with an IonTOF Qtac<sup>100</sup> detector using 3-keV <sup>4</sup>He<sup>+</sup> and 5-keV Ne+ under UHV conditions (base pressure  $< 7 \times 10^{-10}$ mbar). Typical measurements used a target ion current in the range of 3 nA. The ion beam was focused on a 1 mm  $\times$  1 mm sample area at normal incidence. The high surface sensitivity of the technique (~3 monolayers) originates from a unique analyzer detector design, where the large scatter angle (fixed scattering angle = 145°) of detection increases elemental sensitivity, allowing low ion doses (negligible sputtering/ intermixing). Initially, the He<sup>+</sup> LEIS spectra, using a  $\sim 9 \times 10^{13}$  ion/cm<sup>2</sup> dose, were typically dominated by carbon contamination from air-exposure during sample transfer from the ALD reactor to the LEIS instrument, due to the high surface sensitivity of the technique. To address this issue, the samples were lightly sputtered<sup>23</sup> for 120 s using 10<sup>15</sup> Ne<sup>+</sup> ions/cm<sup>2</sup> (5 keV). Sputtering was stopped immediately after the carbon levels, monitored using He<sup>+</sup> ions, were below the LEIS detection limit for carbon (C > 1% of monolayer [10<sup>15</sup>/cm<sup>2</sup>]).<sup>22,23</sup> To better distinguish heavier elements such as Ga, As, and In, Ne<sup>+</sup> ions ( $\sim 7 \times 10^{13}$ /cm<sup>2</sup>) were

Conventional TEM samples were prepared using ion beams in a Helios 600 workstation and examined with a JEOL2100 at 200 kV.

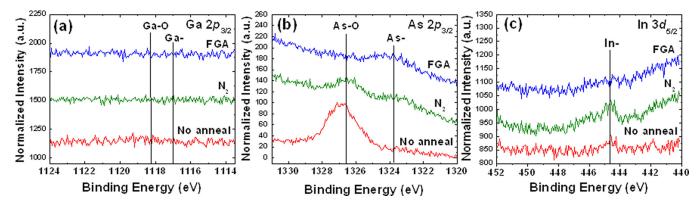

Figure 1 shows the XPS core level spectra of (a) Ga  $2p_{3/2}$ , (b) As  $2p_{3/2}$ , and (c) In  $3d_{5/2}$  for all three HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As samples, untreated, and treated in N2 and FGA at 350°C, respectively. The thickness of the HfO<sub>2</sub> film (4 nm) ensures that the substrate is not detected, as evidenced by the absence of bulk contribution from the any of the core level spectra (Figures 1(a)–1(c)). Considering the relative core level kinetic energy for Ga 2p (binding energy = 1117 eV), the photoelectron kinetic energy is 370 eV and the effective attenuation length (EAL) 0.6 nm, such that the total XPS sampling depth is  $\sim$ 2 nm. <sup>24,25</sup> This indicates that no Ga contribution from the bulk In<sub>0.53</sub>Ga<sub>0.47</sub>As could be observed within the XPS detection limits, so that only Ga located near the top surface region would appear in the spectra. This initial observation establishes a baseline necessary to draw conclusions, if any, of the substrate elements that are detected within or at the surface of the

FIG. 1. XPS core level spectra of (a) Ga  $2p_{3/2}$ , (b) As  $2p_{3/2}$ , (c) In  $3d_{5/2}$  for HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As after post deposition treatment in N<sub>2</sub> (green), FGA (blue), and unannealed samples (red).

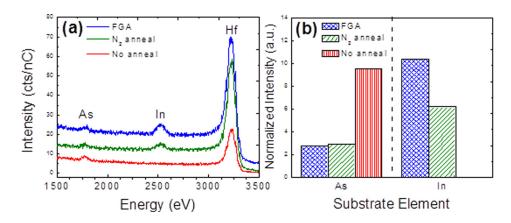

FIG. 2. (a) LEIS spectra and (b) normalized LEIS peak intensities of 5 keV Ne<sup>+</sup> backscattered from HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As after post deposition treatment using FGA, N<sub>2</sub> anneal and no anneal samples of the diffused substrate elements through. Evidence of As and In indicates element at the top most monolayer. No In is detected on the "no annealed" sample. The surface was lightly sputtered prior to analysis.

HfO<sub>2</sub> layer. The fact that an As signal is observed (As 2p) for all three samples after HfO<sub>2</sub> deposition, including on the sample prior to any annealing (Figure 1(a)), indicates that As migrates to the surface *during* the ALD process since electrons from the As 2p level have a slightly smaller effective attenuation length (EAL = 0.45 nm) than electrons from the Ga 2p core level. Since these samples were exposed to atmosphere prior to XPS, any As present at the surface would be expected to oxidize as is seen on the unannealed sample. Upon a post deposition anneal at  $350\,^{\circ}$ C, the As oxide signal is reduced with a corresponding increase of the reduced As. Hydrogen contained in forming gas is clearly more effective to reduce As oxide than N<sub>2</sub>. Overall, there is no evidence that As located at the surface after ALD is removed upon annealing.

In contrast, a slight In  $3d_{5/2}$  signal (close to the XPS detection level) is detected after HfO2 deposition prior to any annealing. This observation suggests that In has partially diffused into the film during the ALD process. Upon annealing at 350 °C in N<sub>2</sub>, the In peak intensifies, suggesting that In continues to outdiffuse from the interfacial layer or the In<sub>0.53</sub>Ga<sub>0.47</sub>As surface through the high-k dielectric. This is also expected for the FGA-treatment at 350 °C but the lower In core level intensity suggests that it may desorb from the surface, since In and As oxides are known to begin to decompose at temperatures as low as 150 °C. 15 The relative position of the diffused elements is best investigated by LEIS, which can only sensitively examine the first few monolayers (<3 monolayers) of the HfO<sub>2</sub>/InGaAs surface, using 5 keV Ne<sup>+</sup> ions. Figure 2 shows (a) LEIS spectra and (b) peak intensities of the ions backscattered from the HfO<sub>2</sub> surface after deposition, N2 annealing and FGA treatments for In and As. All peak intensities are normalized to the Hf peak in order to compare the relative As and In coverages. An intense As signal is observed at the surface after ALD of  $HfO_2$ . This unambiguously shows that part of the As  $2p_{3/2}$ core level electrons observed with XPS in Figure 1(a) originates from the surface. In contrast, no In signal is observed for this unannealed sample, highlighting the difference in mobility between As and In atoms during ALD growth. While In does diffuse into HfO<sub>2</sub>, as evidenced by a very weak In 3d<sub>5/2</sub> core level signal in XPS, it does not reach the near surface region. After the N2 anneal, the normalized As signal intensity is reduced compared to the unannealed sample, suggesting that surface As does desorb from the surface at these temperatures, as postulated above. The appearance of an In signal in the LEIS spectra after annealing is evidence for In diffusion from the HfO2 interfacial region to the surface. Since the XPS measurements of In 3d<sub>5/2</sub> indicate an overall decrease of In, this observation indicates that In has diffused to the surface and part of it desorbed. While this suggests that hydrogen fosters desorption, the role of hydrogen is still not well understood.

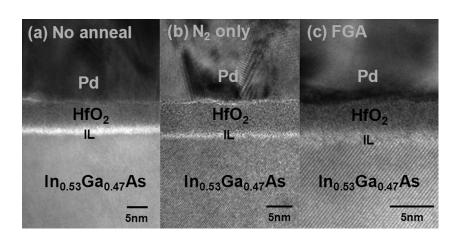

In order to understand the effects of post-deposition annealing on the interfacial structure of the Pd/HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As, conventional TEM images were obtained on all three samples after treatment (Figures 3(a)–3(c)). For the untreated sample, a clear interfacial region is observed between the HfO<sub>2</sub> and In<sub>0.53</sub>Ga<sub>0.47</sub>As. This interfacial layer is most likely composed of native oxides. <sup>20</sup> Importantly, a reduction in the interfacial layer thickness is observed after annealing the HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As stack in N<sub>2</sub> at 350 °C. Further reduction of this interfacial layer is observed when the

FIG. 3. Conventional TEM images of (a) no anneal, (b)  $N_2$  only, and (c) FGA  $Pd/HfO_2/In_{0.53}Ga_{0.47}As$  gate stacks showing the interfacial layer reduction after the post oxide deposition anneal.

#### Unannealed

# As-O As-O As-O In HfO<sub>2</sub> In IL In<sub>0.53</sub>Ga<sub>0.47</sub>As

### N<sub>2</sub> anneal

### **FGA**

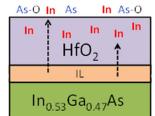

FIG. 4. Schematic representation of the substrate element diffusion through the HfO<sub>2</sub>. The net result of these processes is a reduction of interfacial layer thickness, and potentially a densification of the HfO<sub>2</sub> layer, arising from the ability of excess oxygen to reduce the number of oxygen vacancies in layer HfO<sub>2</sub> layer. A natural consequence of these phenomena should lead to measurable changes in electrical properties

sample undergoes the FGA treatment. These observations are consistent with the loss of elements (by diffusion) observed with XPS and LEIS as well as IR measurements.<sup>26</sup> They support the conclusion that In observed at the surface and near surface region is due to the diffusion from the decomposition of the interfacial layer during post deposition treatments.

Figure 4 schematically illustrates the proposed mechanisms derived from the combined XPS, LEIS, and TEM measurements. First, the unannealed samples display a large concentration of As at the surface of HfO<sub>2</sub> in the form of As oxides, with a corresponding modification of the interfacial layer. This interfacial layer contains less As oxide than the native oxide due to oxygen scavenging during the initial ALD process. The such as depletion is expected to result in a relatively In- and Ga-rich interfacial layer. During N<sub>2</sub> anneal, surface As species are desorbed, most likely in the form of As-O. Concurrently, In originating from the In- and Ga-rich interfacial layer, migrates through the HfO<sub>2</sub> layer to the surface and near surface region.

As previously suggested only from XPS measurements, thermal treatments lead to interfacial layer decomposition and diffusion. <sup>15,17,28</sup> For instance, Suri *et al.* <sup>28</sup> established from *ex-situ* XPS that after depositing an HfO<sub>2</sub> film on native oxide-covered GaAs, no arsenic oxides are observed after a 400 °C rapid thermal anneal for 20 s in a N<sub>2</sub> environment. Their observation is consistent with the well-established chemical reduction of  $As_2O_3$  on GaAs surfaces between the temperatures of 320 °C–400 °C, following the reaction: <sup>29,30</sup>

$$As_2O_3 + 2GaAs \rightarrow Ga_2O_3 + 2As_2(\uparrow)$$

This chemical pathway provides the formation of a strongly bound  $Ga_2O_3$  moiety at the interface, which is a stable oxide in this temperature range. This accounts for a lack of Ga signal in both XPS and LEIS data. Chang *et al.*<sup>31</sup> also observed an increase of the In  $3d_{3/2}$  core level using angle-resolved XPS after depositing ultra-thin (0.8 nm) HfO<sub>2</sub> films by ALD on  $In_{0.2}Ga_{0.8}As$  at  $320\,^{\circ}C$ , which they attributed to In segregation.

In our case, we find that the mobility of the substrate atoms strongly depend on the deposition temperature. At 250 °C deposition temperature, no indium is observed by LEIS at the HfO<sub>2</sub> surface. Upon annealing in nitrogen or forming gas at 350 °C, In diffuses to the HfO<sub>2</sub> surface, in agreement with the observations of Chang *et al.*<sup>31</sup> A further increase in the In concentration after FGA treatment suggests that H<sub>2</sub> also plays a role in the decomposition of the interfacial oxides. Such decomposition gives rise to excess oxygen at the interface, which may naturally migrate to vacancy sites

within the  $HfO_2$  layer<sup>32</sup> and would result in modification (e.g., densification) of the  $HfO_2$  layer itself. The In component, believed to be in the form of  $In-O_x$ , is located within the top most monolayers of the  $HfO_2$  surface since it is easily detected by a highly surface sensitive technique (LEIS). In addition, the relatively more intense indium peak in LEIS after FGA as compared to  $N_2$  anneal is consistent with an accumulation of In at the surface. All these results are consistent with the current observation for  $HfO_2$  films on  $In_{0.53}Ga_{0.47}As$ , suggesting that diffusion is a general phenomenon for high-k dielectric/III-V stacks that are typically characterized by unstable interfaces.

From all these observations, we hypothesize that post annealing, particularly in forming gas, reduces the interfacial layer and potentially decreases the number of oxygen vacancies in the HfO<sub>2</sub> films by oxygen migration from the interface upon In diffusion. To test this hypothesis, C-V measurements were performed using the as-deposited (unannealed) stack as reference. These C-V measurements recorded over a range of frequency and temperature were sufficient to show that the as-deposited HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As stack and subsequently annealed (in N<sub>2</sub> or FGA) samples all exhibit genuine surface accumulation, and that the accumulation capacitance is affected by the annealing process.

The results in Table I illustrate that the post-deposition treatments of HfO<sub>2</sub>/InGaAs gate stacks result in an increase in the maximum capacitance upon N2 anneal and even larger increase upon FGA in the accumulation region at 3 V. The accumulation capacitances in the C-V response for the no anneal, N<sub>2</sub> and FGA samples have the capacitance equivalent thickness (CET) values of 1.92 nm, 1.82 nm, and 1.63 nm, respectively. It is noted that these experiments used intentionally non-optimized stacks in order to highlight interface layer modification and elemental diffusion resulting from post deposition annealing. The interface state density around the mid gap energy  $D_{it}$  was in excess of  $1 \times 10^{13} \text{ cm}^{-2} \text{ eV}^{-1}$  for all samples. Importantly, the leakage was  $<5 \times 10^{-4}$  A/cm<sup>2</sup> over the C-V bias range (±3 V), allowing reliable capacitance extraction for the values reported in Table I. Overall, these results are fully consistent with the observed reduction of interfacial oxide by TEM (see supplementary material<sup>26</sup>).

TABLE I. Maximum capacitances ( $C_{max}$ ) and CET for post deposition-treated  $HfO_2/In_{0.53}Ga_{0.47}As$  samples.

| Sample                                                                   | No anneal    | N <sub>2</sub> only | Forming gas |

|--------------------------------------------------------------------------|--------------|---------------------|-------------|

| $C_{\text{max}}$ @ 1 kHz( $\mu$ F/cm <sup>2</sup> )<br>CET @ = +3 V (nm) | 1.85<br>1.92 | 1.90<br>1.82        | 2.11        |

| CEI $\underline{w} = +3 \text{ V (IIIII)}$                               | 1.92         | 1.62                | 1.05        |

In summary, HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As gate stacks were characterized using LEIS, XPS, and C-V measurements. Transport of As, and to a much lower degree of In, both originating from the initial native oxide, was shown to occur during ALD of HfO2, as evidenced by the detection of As-based oxides in XPS and surface As with LEIS on unannealed samples. No In or Ga was detected on the HfO<sub>2</sub> surface prior to any post-annealing treatments, highlighting the mobility of As compared to these two elements. Clear evidence for In diffusion to the surface only after post-deposition annealing of HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As stacks was provided by XPS and LEIS. TEM images showed that the thickness of the interfacial layer is decreased upon annealing, confirming out-diffusion of metallic elements and suggesting oxygen depletion as well. The overall reduction of the interfacial layer and postulated densification of the HfO<sub>2</sub> layer upon post deposition anneals in N<sub>2</sub> anneal or forming gas is further supported by the observed increase in the maximum capacitance.

The authors would like to acknowledge Professor Chris Hinkle for insightful discussions and Dr. Michael Schmidt and Dr. Patrick Carolan at the Tyndall National Institute for TEM analysis. The authors gratefully acknowledge the financial support of the National Science Foundation as a part of the U.S. –Ireland R&D Partnership (Grant No. NSF-ECCS-0925844), NSF (CHE 1300180) and Science Foundation Ireland [Grant No. 09/IN.1/I2633].

- R. Chau, S. Datta, M. Doczy, B. Doyle, J. Jin, J. Kavalieros, A. Majumdar, M. Metz, and M. Radosavljevic, IEEE Trans. Nanotechnol. 4, 153 (2005).

J. A. del Alamo, Nature 479, 317 (2011).

- <sup>3</sup>E. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, M. E. Pemble, G. Brammertz, M. Heyns, S. B. Newcomb, V. V. Afanas'ev, and P. K. Hurley, Appl. Phys. Lett. **94**, 102902 (2009).

- <sup>4</sup>H. D. Trinh, E. Y. Chang, P. W. Wu, Y. Y. Wong, C. T. Chang, Y. F. Hsieh, C. C. Yu, H. Q. Nguyen, Y. C. Lin, K. L. Lin, and M. K. Hudait, Appl. Phys. Lett. **97**, 042903 (2010).

- <sup>5</sup>R. Suzuki, N. Taoka, M. Yokoyama, S. H. Kim, T. Hoshii, T. Maeda, T. Yasuda, O. Ichikawa, N. Fukuhara, M. Hata, M. Takenaka, and S. Takagi, J. Appl. Phys. **112**, 084103 (2012).

- <sup>6</sup>H. Zhao, Y. T. Chen, J. H. Yum, Y. Z. Wang, F. Zhou, F. Xue, and J. C. Lee, Appl. Phys. Lett. **96**, 102101 (2010).

- <sup>7</sup>C. L. Hinkle, A. M. Sonnet, E. M. Vogel, S. McDonnell, G. J. Hughes, M. Milojevic, B. Lee, F. S. Aguirre-Tostado, K. J. Choi, H. C. Kim, J. Kim, and R. M. Wallace, Appl. Phys. Lett. 92, 071901 (2008).

- <sup>8</sup>M. M. Frank, G. D. Wilk, D. Starodub, T. Gustafsson, E. Garfunkel, Y. J. Chabal, J. Grazul, and D. A. Muller, Appl. Phys. Lett. **86**, 152904 (2005).

- <sup>9</sup>C. H. Chang, Y. K. Chiou, Y. C. Chang, K. Y. Lee, T. D. Lin, T. B. Wu, M. Hong, and J. Kwo, Appl. Phys. Lett. **89**, 242911 (2006).

- <sup>10</sup>K. Onishi, C. S. Kang, R. Choi, H. J. Cho, S. Gopalan, R. E. Nieh, S. A. Krishnan, and J. C. Lee, IEEE Trans. Electron Devices 50, 384 (2003).

- <sup>11</sup>Y. Hwang, R. Engel-Herbert, N. G. Rudawski, and S. Stemmer, J. Appl. Phys. 108, 034111 (2010).

- <sup>12</sup>E. J. Kim, L. Q. Wang, P. M. Asbeck, K. C. Saraswat, and P. C. McIntyre, Appl. Phys. Lett. **96**, 012906 (2010).

- <sup>13</sup>V. Chobpattana, J. Son, J. J. M. Law, R. Engel-Herbert, C. Y. Huang, and S. Stemmer, Appl. Phys. Lett. **102**, 022907 (2013).

- <sup>14</sup>R. D. Long, B. Shin, S. Monaghan, K. Cherkaoui, J. Cagnon, S. Stemmer, P. C. McIntyre, and P. K. Hurley, J. Electrochem. Soc. 158, G103 (2011).

- <sup>15</sup>B. Brennan and G. Hughes, J. Appl. Phys. **108**, 053516 (2010).

- <sup>16</sup>G. K. Dalapati, C. K. Chia, C. C. Tan, H. R. Tan, S. Y. Chiam, J. R. Dong, A. Das, S. Chattopadhyay, C. Mahata, C. K. Maiti, and D. Z. Chi, ACS Appl. Mater. Interfaces 5, 949 (2013).

- <sup>17</sup>G. K. Dalapati, Y. Tong, W. Y. Loh, H. K. Mun, and B. J. Cho, IEEE Trans. Electron Devices **54**, 1831 (2007).

- <sup>18</sup>C. Weiland, P. Lysaght, J. Price, J. Huang, and J. C. Woicik, Appl. Phys. Lett. **101**, 061602 (2012).

- <sup>19</sup>Y. S. Kang, D. K. Kim, K. S. Jeong, M. H. Cho, C. Y. Kim, K. B. Chung, H. Kim, and D. C. Kim, ACS Appl. Mater. Interfaces 5, 1982 (2013).

- <sup>20</sup>R. D. Long, E. O'Connor, S. B. Newcomb, S. Monaghan, K. Cherkaoui, P. Casey, G. Hughes, K. K. Thomas, F. Chalvet, I. M. Povey, M. E. Pemble, and P. K. Hurley, J. Appl. Phys. 106, 084508 (2009).

- <sup>21</sup>R. M. Wallace, in *Physics and Technology of High-K Gate Dielectrics* 6, edited by S. Kar, D. Landheer, M. Houssa, D. Misra, S. VanElshocht, and H. Iwai (Electrochemical Society Inc, Pennington, 2008), Vol. 16, p. 255.

- <sup>22</sup>H. H. Brongersma, M. Draxler, M. de Ridder, and P. Bauer, Surf. Sci. Rep. 62, 63 (2007).

- <sup>23</sup>E. Taglauer and W. Heiland, Appl. Phys. **9**, 261 (1976).

- <sup>24</sup>S. Tanuma, T. Shiratori, T. Kimura, K. Goto, S. Ichimura, and C. J. Powell, Surf. Interface Anal. 37, 833 (2005).

- <sup>25</sup>C. L. Hinkle, M. Milojevic, E. M. Vogel, and R. M. Wallace, Appl. Phys. Lett. **95**, 151905 (2009).

- <sup>26</sup>See supplementary material at http://dx.doi.org/10.1063/1.4860960 for details of reduction in interface layer using attenuated total reflectance infrared spectroscopy and multi-frequency capacitance-voltage analysis of HfO<sub>2</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As gate stacks.

- <sup>27</sup>M. Kobayashi, P. T. Chen, Y. Sun, N. Goel, P. Majhi, M. Garner, W. Tsai, P. Pianetta, and Y. Nishi, Appl. Phys. Lett. 93, 182103 (2008).

- <sup>28</sup>R. Suri, D. J. Lichtenwalner, and V. Misra, Appl. Phys. Lett. **96**, 112905 (2010).

- <sup>29</sup>A. Guillen-Cervantes, Z. Rivera-Alvarez, M. Lopez-Lopez, E. Lopez-Luna, and I. Hernandez-Calderon, Thin Solid Films 373, 159 (2000).

- <sup>30</sup>K. Tone, M. Yamada, Y. Ide, and Y. Katayama, Jpn. J. Appl. Phys. Part 2 31, L721 (1992).

- Y. H. Chang, C. A. Lin, Y. T. Liu, T. H. Chiang, H. Y. Lin, M. L. Huang,

T. D. Lin, T. W. Pi, J. Kwo, and M. Hong, Appl. Phys. Lett. 101, 172104

- <sup>32</sup>S. Guha and V. Narayanan, Phys. Rev. Lett. **98**, 196101 (2007).