| Process flow title                                                                                                                                                   |  |  |                                                |            |                  |                  | Revision      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|------------------------------------------------|------------|------------------|------------------|---------------|

| DTU Nanolab - Solar cell process                                                                                                                                     |  |  |                                                |            |                  |                  | 2.6           |

| <br><b>DTU Nanolab</b><br>National Centre for Nano Fabrication and Characterization |  |  | Contact email                                  |            | Contact persons  |                  | Contact phone |

|                                                                                                                                                                      |  |  | <a href="mailto:jehan@dtu.dk">jehan@dtu.dk</a> |            | Jesper Hanberg   |                  | 45255828      |

|                                                                                                                                                                      |  |  | <a href="mailto:kabi@dtu.dk">kabi@dtu.dk</a>   |            | Karen Birkelund  |                  | 452556436     |

|                                                                                                                                                                      |  |  | <a href="mailto:mmat@dtu.dk">mmat@dtu.dk</a>   |            | Maria Matschuk   |                  | 452555723     |

|                                                                                                                                                                      |  |  | Labmanager group                               | Batch name | Date of creation | Date of revision |               |

|                                                                                                                                                                      |  |  | -                                              | May 2024   | 24 May 2016      | 13-Jan-25        |               |

## Objective

This process was originally used in the UV-lithography Green Belt course organized by DTU Nanolab (in 2016). This is an updated version (April 2024). The purpose is to provide an example process flow and to educate Cleanroom users in general UV-lithographic techniques. The outcome are test wafers with solar cells.

| Substrates |         |      |             |        |           |     |               |   |           |

|------------|---------|------|-------------|--------|-----------|-----|---------------|---|-----------|

| Substrate  | Orient. | Size | Doping/type | Polish | thickness | Box | Purpose       | # | Sample ID |

| Silicon    | <100>   | 4"   | p(Boron)    | SSP    | 525±25µm  |     | Device wafers | 6 | S1-S6     |

| Silicon    | <100>   | 4"   | p (Boron)   | SSP    | 525±25µm  |     | Test wafers   | 4 | T1-T4     |

| Silicon    | <100>   | 4"   | p (Boron)   | SSP    | 525±25µm  |     | Dummy wafers  | 2 | D1-D3     |

\* Test wafers: T1-T4 used for quality control (measurements) in between process steps

Dummy wafers: D1-D3 are used to measure furnace performance (from RCA shelf)

Other dummy wafers: need to be purchased and can be used (if wanted) to improve the uniformity in furnace processes

## Figures

| Figure | Caption                                               | Step | Figure                                                                               |

|--------|-------------------------------------------------------|------|--------------------------------------------------------------------------------------|

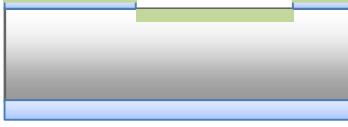

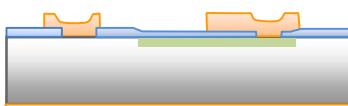

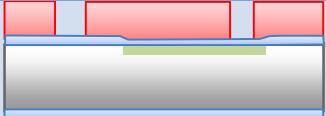

| 1      | After SiO <sub>2</sub> oxidation                      | 1.2  |  |

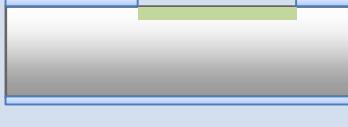

| 2      | After Spin coating                                    | 2.3  |  |

| 3      | After UV lithography<br>(mask layer 1: N+ doped area) | 2.5  |  |

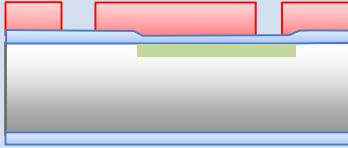

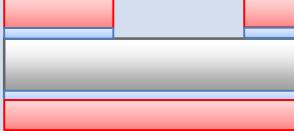

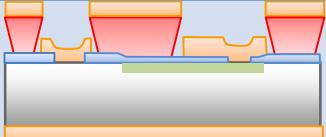

| 4      | After SiO <sub>2</sub> etch in BHF                    | 3.1  |  |

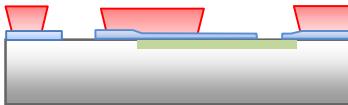

| 5      | After Strip resist                                    | 3.4  |  |

|                                         |            |                  |                     |

|-----------------------------------------|------------|------------------|---------------------|

| Process flow title                      | Rev.       | Date of revision | Contact email       |

| <b>DTU Nanolab - Solar cell process</b> | <b>2.6</b> | <b>13-Jan-25</b> | <b>jehan@dtu.dk</b> |

|    |                                               |      |                                                                                      |

|----|-----------------------------------------------|------|--------------------------------------------------------------------------------------|

| 6  | After Phosphor predep                         | 4.2  |    |

| 7  | After SiO2 etch in BHF                        | 4.3  |    |

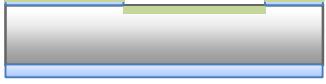

| 8  | After thermal oxidation of SiO2               | 4.5  |    |

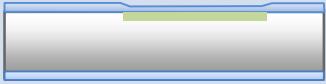

| 9  | After UV lithography (mask layer 2: contacts) | 6.3  |    |

| 10 | After SiO2 etch in BHF                        | 7.2  |   |

| 11 | After resist strip                            | 7.4  |  |

| 12 | After lithography (mask layer 3: metal)       | 8.4  |  |

| 13 | After metal deposition                        | 9.2  |  |

| 14 | After lift-off                                | 9.34 |  |

|                                                               |                    |                                      |                                      |

|---------------------------------------------------------------|--------------------|--------------------------------------|--------------------------------------|

| Process flow title<br><b>DTU Nanolab - Solar cell process</b> | Rev.<br><b>2.6</b> | Date of revision<br><b>13-Jan-25</b> | Contact email<br><b>jehan@dtu.dk</b> |

|---------------------------------------------------------------|--------------------|--------------------------------------|--------------------------------------|

| Step Heading                                                                                                                                | Equipment                  | Procedure                                                                                                                                                                                                                                                                                                                                  | Comments                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>1 SiO<sub>2</sub> Dry Oxidation</b><br>(Creating SiO <sub>2</sub> protection layer (and insulator/protection) for areas not to be doped) |                            |                                                                                                                                                                                                                                                                                                                                            | <b>Wafer S1-S6, T1-T3, D1 from Nanolab, 2 dummy wafer</b>                                                                                                                                                         |

| 1.1 RCA clean                                                                                                                               | RCA bench                  | Follow standard procedure.                                                                                                                                                                                                                                                                                                                 | All wafers, incl dummies need to be RCA cleaned                                                                                                                                                                   |

| 1.2 SiO <sub>2</sub> dry oxidation                                                                                                          | Boron Drive-in (A1)        | Place D1 in the center of the boat and place device and test wafers equally distributed on each side of D1. No spacing between wafers. Place two dummy wafer on each side outermost (to improve uniformity).<br><i>Target thickness: 150±10nm</i><br><br><u>Recipe: Dry1050</u><br><i>Oxidation time: 170 min</i><br><i>Anneal: 20 min</i> |                                                                                                                                                                                                                   |

| <b>2 UV Lithography– 1.5µm AZ5214E</b><br>(Create mask for doping of active areas)                                                          |                            |                                                                                                                                                                                                                                                                                                                                            | <b>Wafer S1-S6</b>                                                                                                                                                                                                |

| 2.1 Surface treatment                                                                                                                       | Oven HMDS-2                | Coat all wafers with HMDS<br><br><u>Recipe: program 01</u><br><i>Time: ca. 30 min</i>                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                   |

| 2.2 Spin Coating - backside -                                                                                                               | Spin Coater: UV Gamma      | Coat backside of the device wafers with 1.5 µm AZ 5214E resist<br><br><u>Recipe: 3412 DCH 100 mm AZ 5214E 1.5 µm prox bake</u><br><i>Spin-off time: 50-60 s</i><br><i>Soft Bake Temp: 100°C (proximity)</i><br><i>Soft-Bake time: 65 sec</i><br><i>without HMDS</i>                                                                        | Check Spinner nozzle and clean with dummy wafer (if required)                                                                                                                                                     |

| 2.3 Spin Coating - frontside -                                                                                                              | Spin Coater: UV Gamma      | Coat frontside of the device wafers with 1.5 µm AZ5214E resist<br><br><u>Recipe: 3412 DCH 100 mm AZ 5214E 1.5 µm prox bake</u><br><i>Spin-off time: 50-60 s</i><br><i>Soft Bake Temp: 100°C (proximity)</i><br><i>Soft-Bake time: 65 sec</i><br><i>without HMDS</i>                                                                        |                                                                                                                                                                                                                   |

| 2.4 Exposure                                                                                                                                | Maskless Aligner 3 (MLA-3) | <b>Mask layer: "layer 1 - N+ doped areas"</b><br><br><i>Mode: Quality (ca. 15-25 min), Fast (8-10 min)</i><br><i>Dose: 105 mJ/cm<sup>2</sup></i><br><i>Defocus: 2</i><br><i>Laser: 375 nm</i>                                                                                                                                              | <i>Note: 405 nm require increased dose; dose and defoc not very critical for solar cell design itself</i><br><br><i>MA6 Aligner: mask: "n+ doped", Alignment to marks on wafer, Hard contact, duration: 5 sec</i> |

| 2.5 Develop                                                                                                                                 | TMAH UV-lithography        | Develop exposed resist in TMAH<br><br><u>Recipe: 1002 DCH 100 mm SP60s</u><br><i>Dev time: 60 s</i>                                                                                                                                                                                                                                        |                                                                                                                                                                                                                   |

| 2.6 Inspection                                                                                                                              | Optical microscope         | Check pattern and alignment marks                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                   |

|                                                               |                    |                                      |                                      |

|---------------------------------------------------------------|--------------------|--------------------------------------|--------------------------------------|

| Process flow title<br><b>DTU Nanolab - Solar cell process</b> | Rev.<br><b>2.6</b> | Date of revision<br><b>13-Jan-25</b> | Contact email<br><b>jehan@dtu.dk</b> |

|---------------------------------------------------------------|--------------------|--------------------------------------|--------------------------------------|

|                                                                                                            |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>3 SiO<sub>2</sub> Wet Etch</b><br><i>(Remove SiO<sub>2</sub> in unmasked areas (areas to be doped))</i> |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>Wafer S1-S6</b>                                                                                                                                                                                  |

| 3.1 SiO <sub>2</sub> etch                                                                                  | Oxide etch 2: BHF<br>(Wet bench 04)   | Etch SiO <sub>2</sub> in exposed areas in BHF. Etching rate: 75-80 nm/min. Rinse in DI water.<br><br><i>Etch time: 2-2½ min</i><br><i>DI rinse: 5 min ± 30 sec</i>                                                                                                                                                                                                                                                                                                                                 |                                                                                                                  |

| 3.2 Drying                                                                                                 | Spin dryer                            | Transfer wafer box into spin dryer                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                     |

| 3.3 Inspection                                                                                             | Optical microscope                    | Check pattern and alignment marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                     |

| 3.4 Strip resist                                                                                           | Plasma Asher 4<br>(Resist Strip)      | <i>Recipe: 18</i><br><i>Time: 30 min</i><br><i>O2 flow: 400</i><br><i>N2 flow: 70</i><br><i>Power: 1000 W</i>                                                                                                                                                                                                                                                                                                                                                                                      | <i>Alternative Resist Strip: 10 min</i><br>                                                                      |

| 3.5 Inspection                                                                                             | Dektak XTA                            | Measure step height of one or two device wafers<br>Target: 150±10 nm                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>Wafer S1-S6</b><br>Note in measurement sheet                                                                                                                                                     |

| <b>4 Phosphor Doping</b><br><i>(Doping with phosphor - silicon in "open areas")</i>                        |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>Wafer S1-S6, T1-T4, D2-D3</b><br>from Nanolab, 2 dummy wafer                                                                                                                                     |

| 4.1 RCA clean                                                                                              | RCA bench                             | Follow standard procedure but <u>without HF dip</u> .<br>All wafers, incl dummies need to be RCA cleaned                                                                                                                                                                                                                                                                                                                                                                                           | <b>Wafer S1-S6, T1-T4, D2-D3, 4 dummy wafer</b><br>(D2 for A4-furnace, D3 for A3-furnace)<br><u>No HF</u><br>RCA clean 4 dummy wafers for A4 (2) and A3 (4). Dummies from A4 can be re-used for A3. |

| 4.2 Phosphor doping<br>(gas: POCl <sub>3</sub> )                                                           | Furnace:<br>Phosphorus<br>Predep (A4) | Place D2 in the center of the boat and place device and test wafers equally distributed on each side of D2. No spacing between wafers. Front-side to the left. Place one new dummy wafer on each side outermost to device wafers (to prevent unintended doping from "used" dummy). Place two dummy wafers on each side outmost (to improve uniformity).<br><br>Target doping : R <sub>sheet</sub> =40 Ω <sup>2</sup><br><br><i>Recipe: POCL950</i><br><i>Time: 15 min</i><br><i>Anneal: 20 min</i> | <b>Wafer S1-S6, T1, T4, D2, 2 dummy wafers</b><br><br>Note diffusion time in furnace A4-logbook<br>            |

| 4.3 Measure resistivity                                                                                    | 4 Point Probe                         | Measure resistivity on D2                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Note in measurement sheet.<br>Fill out furnace A4-logbook (with D2).                                                                                                                                |

| 4.4 Etch of phosphor glass for doped wafers                                                                | BHF in RCA bench                      | Removes all phosphor glass and only some of the dry oxide.<br><br><i>Time: exactly 30 sec</i>                                                                                                                                                                                                                                                                                                                                                                                                      | <b>Wafer S1-S6, T1, T2</b><br><i>Note that the wafer becomes hydrophobic.</i><br>                              |

| Process flow title<br><b>DTU Nanolab - Solar cell process</b>                                                                                |                                      |                                                                                                                                                                                                                                                                                                                                                                | Rev.<br><b>2.6</b>                                                                                                                                  | Date of revision<br><b>13-Jan-25</b> | Contact email<br><b>jehan@dtu.dk</b>                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.5 Inspection                                                                                                                               | FilmTek 4000<br>(alt. Ellipsometer)  | Measure remaining oxide thickness of T1 and T2 and calculate how much Phosphorglass/doped SiO <sub>2</sub> and SiO <sub>2</sub> has been etched.<br><br>Target thickness: 150 – 70 ±10 nm                                                                                                                                                                      | Note in measurement sheet.                                                                                                                          |                                      |                                                                                                                                                          |

| <b>5 SiO<sub>2</sub> Dry Oxidation</b><br>(Creating SiO <sub>2</sub> insulation layer)                                                       |                                      |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                     |                                      | <b>Wafer S1-S6, T3, T4, D3</b>                                                                                                                           |

| 5.1 SiO <sub>2</sub> dry oxidation                                                                                                           | Phosphor Drive-in (A3)               | Place D3 in the center of the boat and place device and test wafers equally distributed on each side of D3. Front-side to the left. No spacing between wafers. Place two dummy wafer on each side outermost (to improve uniformity).<br><br>Target thickness: 90 ±10nm<br><br><u>Recipe: Dry1050</u><br><i>Oxidation time: 75 min</i><br><i>Anneal: 20 min</i> | <b>Wafer S1-S2, T3, T4, D3, 2 dummy wafers</b>                                                                                                      |                                      | Note result in the furnace log (D2) and in measurement sheet.<br><br> |

| 5.2 Inspection                                                                                                                               | FilmTek 4000 (Ellipsometer)          | Measure oxide final thickness.<br>Target thickness: 90 ±10 nm (dummy D3)<br><br>T3 (80+90 ±10 nm)<br><br>T4 (ca. 90 ±10 nm)                                                                                                                                                                                                                                    | Fill out A3-furnace logbook.<br><i>Note: This measurement cannot be done between both furnaces (A4 and A3), else another RCA is required.</i>       |                                      |                                                                                                                                                          |

| 5.3 Measure resistivity                                                                                                                      | 4 Point Probe                        | Measure resistivity on T4                                                                                                                                                                                                                                                                                                                                      | Note in measurement sheet                                                                                                                           |                                      |                                                                                                                                                          |

| <b>6 UV Lithography – 1.5µm AZ5214E</b><br>(Create mask for etching of SiO <sub>2</sub> to open “free access” to silicon for metal contacts) |                                      |                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                     |                                      | <b>Wafer S1-S6</b>                                                                                                                                       |

| 6.1 Spin Coating - frontside -                                                                                                               | Spin Coater: Gamma UV                | Coat the wafers with 1.5 µm positive resist AZ5214E (Spin-off: 30-60 s; Soft Bake at Temp: 90°C, time: 90 sec)<br><br><u>Recipe: 3411 DCH 100mm 5214E 1.5um HMDS</u><br><i>Spin-off time: 55 s</i><br><i>Soft Bake Temp: 100°C (proximity)</i><br><i>Soft-Bake time: 65 sec</i><br><i>without HMDS</i>                                                         |                                                                                                                                                     |                                      |                                                                                                                                                          |

| 6.2 Exposure                                                                                                                                 | Maskless Aligner MLA-3 (MLA-2, MA-6) | <b>Mask layer: “layer 2 - contacts”</b><br><br><i>Mode: Quality (ca. 20-25 min), Fast (4-7 min)</i><br><i>Dose: 105 mJ/cm<sup>2</sup></i><br><i>Defocus: 2</i><br><i>Laser: 375 nm</i><br><i>Alignment: check location for alignment marks in design file</i>                                                                                                  | <i>Note: 405 nm requires increased dose</i><br><br><i>MA6 Aligner: mask: “contacts”, Alignment to marks on wafer, Hard contact, duration: 5 sec</i> |                                      |                                                                                                                                                          |

| 6.3 Develop                                                                                                                                  | Developer: TMAH UV-Lithography       | Develop in TMAH<br><u>Recipe: 1002 DCH 100 mm SP60s</u><br><i>Dev time: 60 s</i>                                                                                                                                                                                                                                                                               |                                                                |                                      |                                                                                                                                                          |

| 6.4 Inspection                                                                                                                               | Optical microscope                   | Check pattern and alignment                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                     |                                      |                                                                                                                                                          |

|                                                               |                    |                                      |                                      |

|---------------------------------------------------------------|--------------------|--------------------------------------|--------------------------------------|

| Process flow title<br><b>DTU Nanolab - Solar cell process</b> | Rev.<br><b>2.6</b> | Date of revision<br><b>13-Jan-25</b> | Contact email<br><b>jehan@dtu.dk</b> |

|---------------------------------------------------------------|--------------------|--------------------------------------|--------------------------------------|

| <b>7 SiO<sub>2</sub> Wet Etch</b><br>(Etching of SiO <sub>2</sub> to open "free access" to silicon for metal contacts) |                                   |                                                                                                                                                                                                                                                                   | <b>Wafer S1-S6</b>                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7.1 SiO-etch                                                                                                           | Oxide etch 2: BHF                 | Etch SiO <sub>2</sub> in exposed areas in BHF. Etching rate: 75-80 nm/min. Rinse in DI water.<br><br><i>Etch time: 2-2½ min</i><br><i>DI rinse: 5 min ± 30 sec</i>                                                                                                | Note that the backside becomes hydrophobic.                                                                                                                   |

| 7.2 Drying                                                                                                             | Spin dryer                        | Transfer wafer box into spin dryer                                                                                                                                                                                                                                |                                                                            |

| 7.3 Inspection                                                                                                         | Optical microscope                | Check pattern and alignment                                                                                                                                                                                                                                       |                                                                                                                                                               |

| 7.4 Strip resist                                                                                                       | Plasma Asher 2                    | <u>Recipe: 18</u><br><i>Time: 30 min</i><br><i>O2 flow: 400</i><br><i>N2 flow: 70</i><br><i>Power: 1000 W</i>                                                                                                                                                     |                                                                            |

| 7.5 Inspection                                                                                                         | Dektak XTA                        | Measure step height between Si-P (N+) and SiO <sub>2</sub> on device wafers<br><br>Target: 90±10 nm in N+ areas<br>Target: 130±10 nm in un-doped areas                                                                                                            |                                                                                                                                                               |

| <b>8 Lithography – 2.0µm n-LOF2020</b><br>(Create mask for deposition and lift-off for metal contacts)                 |                                   |                                                                                                                                                                                                                                                                   | <b>Wafer S1-S6</b>                                                                                                                                            |

| 8.1 Coat Wafers                                                                                                        | Spin Coater:<br>Gamma UV          | Coat the wafers with 2.0 µm negative resist nLOF 2020<br><br><u>Recipe: 2420 - DCH 100mm nLOF 2020 2 um</u><br><i>Soft Bake temp: 110°C</i><br><i>Soft Bake time: 60 sec</i>                                                                                      |                                                                                                                                                               |

| 8.2 Transport of wafers                                                                                                | non-transparent transport box     | Transport wafers inside a black or blue transport box                                                                                                                                                                                                             | To avoid unwanted exposure from the white light in the cleanroom.                                                                                             |

| 8.3 Exposure                                                                                                           | MLA-2 (MA-6)                      | <b>Mask layer: "layer 3 - metal"</b><br><br><i>Mode: Quality (ca. 45 min), Fast (ca. 20-25 min)</i><br><i>Dose: 550 mJ/cm<sup>2</sup></i><br><i>Defocus: 0</i><br><i>Laser: 375 nm (!)</i><br><i>Alignment: check location for alignment marks in design file</i> | <i>Note: nLoF 2020 requires MLA-2 due to wavelength;</i><br><br><i>MA6 Aligner: mask: "metal", Alignment to marks on wafer, Hard contact, duration: 5 sec</i> |

| 8.4 Post Exposure Bake and Develop                                                                                     | Developer: TMAH<br>UV-Lithography | Post Exposure Bake and Development<br><br><u>Recipe: 3001 DCH 100mm PEB60s@110C+SP60s</u><br><i>PEB temp: 110°C</i><br><i>PEB time: 60 sec;</i><br><i>Dev time: 60 s</i>                                                                                          | Fill out the logbook.<br><br>                                            |

| 8.5 Inspection                                                                                                         | Optical microscope                | Alignment check                                                                                                                                                                                                                                                   |                                                                                                                                                               |

|                                                               |                    |                                      |                                      |

|---------------------------------------------------------------|--------------------|--------------------------------------|--------------------------------------|

| Process flow title<br><b>DTU Nanolab - Solar cell process</b> | Rev.<br><b>2.6</b> | Date of revision<br><b>13-Jan-25</b> | Contact email<br><b>jehan@dtu.dk</b> |

|---------------------------------------------------------------|--------------------|--------------------------------------|--------------------------------------|

| <b>9 Aluminum pattern</b><br><i>(Deposition of metal contacts)</i> |                                |                                                                                                                                                                                                           |                                                                                     |

|--------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| <b>Wafer S1-S6</b>                                                 |                                |                                                                                                                                                                                                           |                                                                                     |

| 9.1 Aluminum deposition - frontside -                              | E-Beam Evaporator (Temescal)   | Deposition of Titanium and Aluminum on front side<br><i>Thickness: 50 nm Ti + 300 nm Al</i>                                                                                                               | Titanium acts as barrier layer to avoid diffusion of aluminum into silicon          |

| 9.2 Aluminum deposition - backside -                               | E-Beam Evaporator - 10 pockets | Deposition of Aluminum on back side<br><i>Thickness: 300 nm Al</i>                                                                                                                                        |  |

| 9.3 Lift-off                                                       | Lift-off (D-3)                 | Remove resist using Remover 1165 for 2-3 min.<br>Temperature: 45 °C. Start the ultrasound for 10 min.<br>Rotate wafers and start ultrasound for another 10 min. Rinse in DI water for 5 min (300±30 sec). | Fill out the logbook.                                                               |

| 9.4 Drying                                                         | Spin dryer                     | Transfer wafer box in dedicated transport box (single green or yellow dots) into spin dryer                                                                                                               |  |

| 9.5 Inspection                                                     | Optical microscope             | Check for complete lift-off                                                                                                                                                                               |                                                                                     |

| 9.6 Annealing                                                      | Furnace: Al Anneal (C4)        | Anneal wafers for 15min at Temp: 400 °C<br><i>Recipe: ANN400</i>                                                                                                                                          | Fill out the logbook.                                                               |

| 9.7 Inspection                                                     | Dektak                         | Measure thicknesses (on front and back).                                                                                                                                                                  |                                                                                     |

| 9.8 Inspection                                                     | 4 Point Probe                  | Measure metal sheet resistance on backside.                                                                                                                                                               |                                                                                     |

|                                                               |                    |                                      |                                      |

|---------------------------------------------------------------|--------------------|--------------------------------------|--------------------------------------|

| Process flow title<br><b>DTU Nanolab - Solar cell process</b> | Rev.<br><b>2.6</b> | Date of revision<br><b>13-Jan-25</b> | Contact email<br><b>jehan@dtu.dk</b> |

|---------------------------------------------------------------|--------------------|--------------------------------------|--------------------------------------|

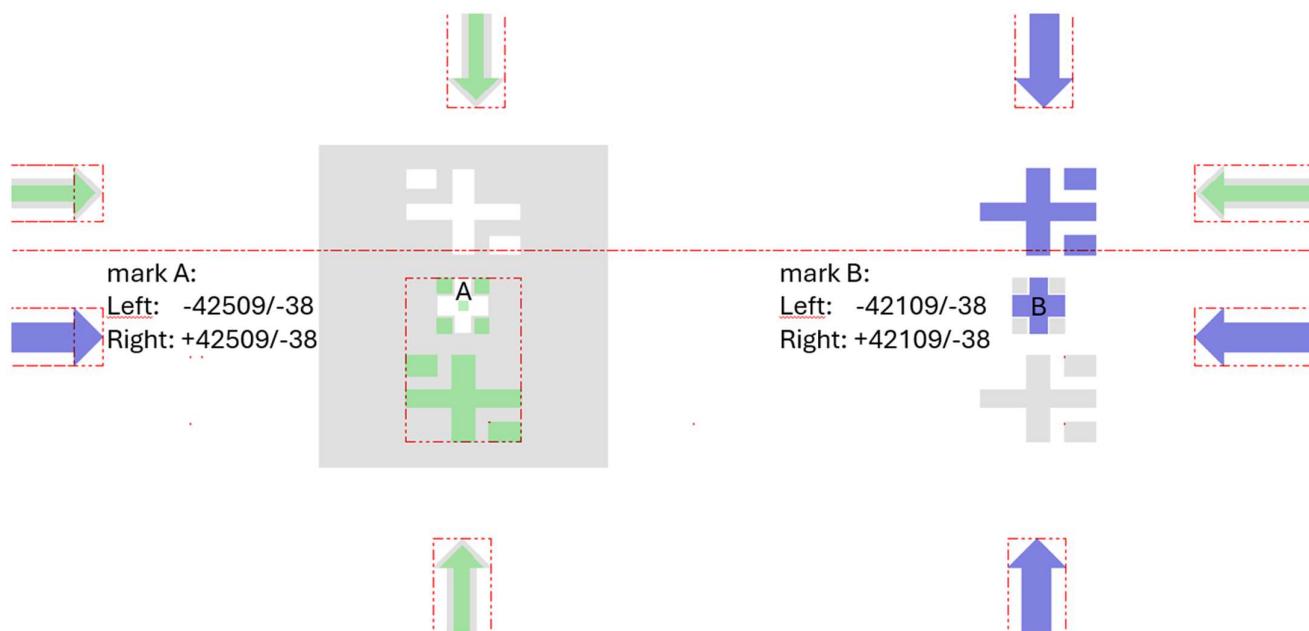

## Alignment Marks